仿真擴展芯片(EEC)簡化高速汽車嵌入式處理器的集成

仿真設備使用一個原始生產器件的宏指令,完成所有的一般性功能、外設及端口,接著在外緣添加一個512K的靜態隨機存取存儲器(SRAM)、幾個總線觀察模塊(BOB)及一個擁有一些本地存儲器來控制仿真器的局部CPU(在此情況下為另一PCP 2)。若干高速串口,包括USB、JTAG和Micro- Link端口提供了外部連接口。該附加的線路,也叫EEC(仿真擴展芯片),在大規模生產器件發生改變時,使得仿真器很容易被重新設計,因為互連點并沒有發生變化。

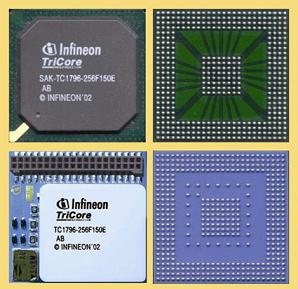

本文引用地址:http://cqxgywz.com/article/85220.htm傳統的外綁器件的另一常見問題在于封裝的大小。仿真設備被特別設計成與標準的生產器件占位面積相符合,并且擁有一組額外添加的針腳來提供更多的信號。同時,還給封裝直接添加了一個頂端連接,通過可移動的連接器就可以采集相同的信號,下方圖象分別顯示了大規模生產器件封裝(頂端)及仿真設備封裝(底端)。

仿真設備甚至提供了比傳統的ICE更多的性能,這些性能包括:

跟蹤性能:

TriCore程序、數據及狀況跟蹤;

PCP程序、數據及線路跟蹤;

所有控制多個組件的主線全方位的可視性;

緩沖器跟蹤數據的優化壓縮;

所有的跟蹤在時間上都全面地得到校正;

中央時標單元;

事件前后跟蹤緩沖(邏輯分析儀)

觸發邏輯性能:

觸發器能夠用于觸發中斷、跟蹤限制及開始/停止跟蹤;

用于控制指令時針及數據地址的范圍比較器;

用于控制數據掩模對等/范圍比較器;

附加的外部事件輸入(2)及輸出(4);

用于計算事件、并在計算和時間基礎上進行時間測量及事件生成的計數器;

同時地、有選擇性地開始和停止所有內核存儲器的中央機制;

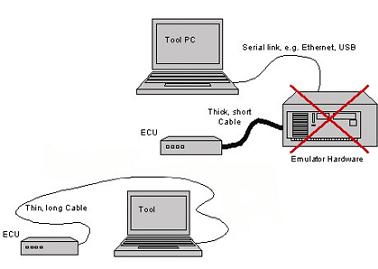

仿真器同時也提供了特殊的重啟模式,通過各種重啟進行調試和校準,開機重啟除外(見下圖)。

仿真設備將仿真器功能嵌入目標應用的生產器件封裝中,因此,外置仿真器硬件不再為人們所需。

EEC中512Kb SRAM是由許多能夠配置的零碎存儲空間組合而成的,這些零碎的存儲空間能夠被任意指派不同的任務。這使單一器件能夠使用于不同的應用情況中。這些功能包括:

—邏輯分析儀模式:SRAM用于(與壓縮規則系統同時)跟蹤任一內部總線及內核存儲器的程序及數據流程。

—軟件開發模式:SRAM用于存儲程序代碼,避免改變時產生老化的閃存,同時允許無限的基于軟件之上的斷點的存在。

—校正標定:SRAM用于暫時存儲所需的校正常量。當發生存取時,校正標定硬件將取數方向由內部閃存轉變為EEC SRAM。外置校正工具能夠通過USB接口或JTAG接口來對SRAM的零碎存儲空間進行快速靈活的讀寫。

—快速制作原型:SRAM作為外置快速原型硬件和微控制器之間的消息緩沖器。由于延遲時間要求低于3ms,USB接口不適于此項任務,因此可以使用MicroLink端口或JTAG接口(延遲時間約為2us,帶寬約為3Mbps)。

—“飛行”記錄儀:SRAM用于記錄系統中使用的數據,或用于跟蹤發生特定錯誤時系統的情況。

仿真設備是由主機PC在運行時配置而成的,該接口受到嚴格的規定,因此各種軟件工具能夠基于同一標準進行互操作。NEXUS并行的、基于總線的跟蹤端口在此不能直接應用,因此只能重新使用軟件編程接口(API)。支持仿真概念的軟件提供了一個器件存取服務器(DAS)。該接口允許多個工具例程裝于一臺PC 中,以共享與嵌入式主機(USB、JPAG)相連的單一通信路徑。DAS同樣允許多個處理器例程與內置的嵌入式主機相連。因此,在將來,也可以訪問更大規模的系統級芯片器件。DAS也支持外在控制協議(XPC)標準,該協議使校準和記錄工具能夠與物理連接媒介獨立地連接起來(CAN、FlexRay、 USB、JTAG)。

由于時鐘速度的加快,高度集成的系統級芯片微控制器的調試和校準只會變得更加的困難。使用一個嵌入式仿真設備能夠為軟件工程師們提供微控制器內部工作情況的可視性,確保系統軟件在現實世界任何條件下都有正確而強大的功能。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論