高性能計算和人工智能正在形成推動半導體行業飛速發展的雙翼。面對摩爾定律趨近極限的挑戰,3DIC Chiplet先進封裝異構集成系統越來越成為產業界矚目的焦點。這種創新的系統不僅在Chiplet的設計、封裝、制造、應用等方面帶來了許多突破,同時也催生了全新的Chiplet EDA平臺,共同為創造下一代數字智能系統賦能。芯和半導體,作為國內首家推出“3DIC Chiplet先進封裝設計分析全流程”EDA平臺的EDA公司,在10月25日上海舉辦了2023芯和半導體用戶大會,總規模超過600人。大會以“極速智能,

關鍵字:

芯和半導體 3DIC Chiplet Chiplet

2023芯和半導體用戶大會以“極速智能,創見未來”為主題,以“系統設計分析”為主線,以“芯和Chiplet

EDA設計分析全流程EDA平臺”為旗艦,包含主旨演講和技術分論壇兩部分,主題涵蓋芯片半導體與高科技系統領域的眾多前沿技術、成功應用與生態合作方面的最新成果。

關鍵字:

芯和半導體 AI HPC Chiplet

半導體周要聞2023.9.28-2023.10.61. 英特爾決戰2nm,4年追趕5代制程,與臺積電維持競合關系明年底,英特爾將推進至18A制程,挑戰臺積電2nm制程,并將用于2025年推出的服務器處理器產品上。英特爾認為,屆時將用比超微更佳的制程奪回市場。臺積電則預計于2025年量產2nm制程芯片。基辛格宣告英特爾下一代制程20A將在明年上半年推出。A代表埃米,一埃米是10分之1nm,20A代表的即是2nm制程。由于電晶體的體積極小,因此,英特爾將改采用GAA(閘極全環電晶體)技術設計的新型電晶體「Ri

關鍵字:

臺積電 chiplet 英特爾

英特爾 CEO 帕特·基辛格:英特爾正在開創人工智能電腦的新時代。

關鍵字:

英特爾 Chiplet

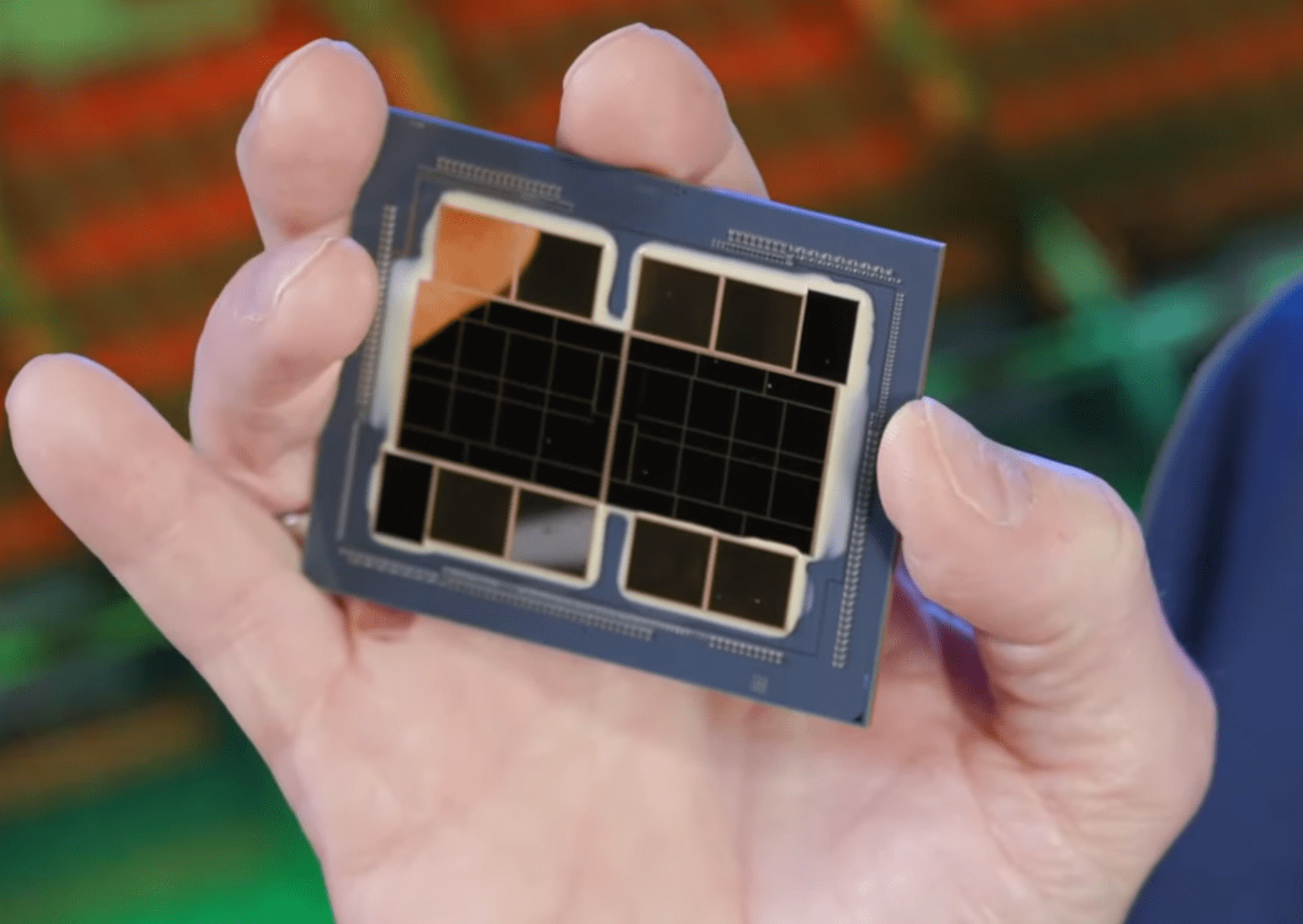

IT之家 9 月 20 日消息,英特爾 CEO 帕特?基辛格 (Pat Gelsinger) 在 Innovation 2023 活動上展示了全球首款基于 UCIe 連接 Chiplet(芯粒)的處理器。這顆代號為“Pike Creek”的測試芯片薈聚了兩大代工廠最尖端工藝,包括基于 Intel 3 工藝的 Intel UCIe IP 小芯片,以及 TSMC N3E 的 Synopsys(新思科技)UCIe IP 小芯片,兩個小芯片之間則通過英特爾 EMIB 接口進行通信。UCIe(U

關鍵字:

英特爾 Chiplet

Chiplet 使英特爾 PSG 能夠為其 FPGA 添加許多新功能

關鍵字:

Chiplet 英特爾

高性能FPGA芯片和嵌入式FPGA IP(eFPGA?IP)領域內的先鋒企業Achronix半導體公司日前宣布:為幫助用戶利用先進的Speedcore eFPGA IP來構建先進的chiplet解決方案,公司開通專用網頁介紹相關技術,以幫助用戶快速構建新一代高靈活性、高性價比的chiplet產品, chiplet設計和開發人員可以透過該公司網站獲得有關Speedcore eFPGA IP的全面支持。中國客戶亦可以通過Achronix在中國的服務團隊得到同樣的支持。Speedcore??

關鍵字:

Achronix FPGA Chiplet

7月11日消息,人工智能熱潮推動芯片制造商加速堆疊芯片設計,就像高科技的樂高積木一樣。業內高管稱,這種所謂的Chiplet(芯粒)技術可以更輕松地設計出更強大的芯片,它被認為是集成電路問世60多年以來最重要的突破之一。IBM研究主管達里奧·吉爾(Darío Gil)在接受采訪時表示:“封裝和Chiplet技術是半導體的未來重要組成部分。”“相比于從零開始設計一款大型芯片,這種技術更加強大。”去年,AMD、英特爾、微軟、高通、三星電子和臺積電等科技巨頭組成了一個聯盟,旨在制定Chiplet設計標準。英偉達,

關鍵字:

AI 芯片制造 Chiplet 臺積電 人工智能

2023年7月3日,中國 北京訊 —— 全球先進的自動測試設備供應商泰瑞達(NASDAQ:TER)宣布,受邀出席了SEMICON China 2023同期舉辦的“先進封裝論壇 - 異構集成”活動。在活動中,泰瑞達Complex SOC事業部亞太區總經理張震宇發表題為《異構集成和Chiplet時代下,芯片測試行業的機遇與挑戰》的精彩演講,生動介紹泰瑞達對于先進封裝,在質量和成本之間找到平衡和最優方案的經驗和見解。 SEMICON China是中國最重要的半導體行業盛事之一,見證中國半導體制造業的茁

關鍵字:

泰瑞達 SEMICON China 異構集成 Chiplet

Chiplet 面臨的安全挑戰之大令人望而生畏。

關鍵字:

Chiplet

從整個芯片的發展來看,隨著芯片工藝制程提升的難度越來越大,Chiplet這種小芯片疊加的方案,已經逐漸成為了一種主流。特別是5nm以下先進芯片工藝,在制造單芯片產品之際成本極高,所以用Chiplet的方案不但能保證性能,同時也能有效節約成本。目前整個行業都在向Chiplet方向發展,甚至海外還有專門針對Chiplet這一技術的聯盟——UCIe聯盟。UCIe聯盟的初衷是確保來自不同供應商的小芯片相互兼容,畢竟多芯片設計的優勢之一是它們可以由不同的公司設計,并由不同的代工廠在不同的節點生產。這樣要做到不同芯片

關鍵字:

Chiplet 小芯片

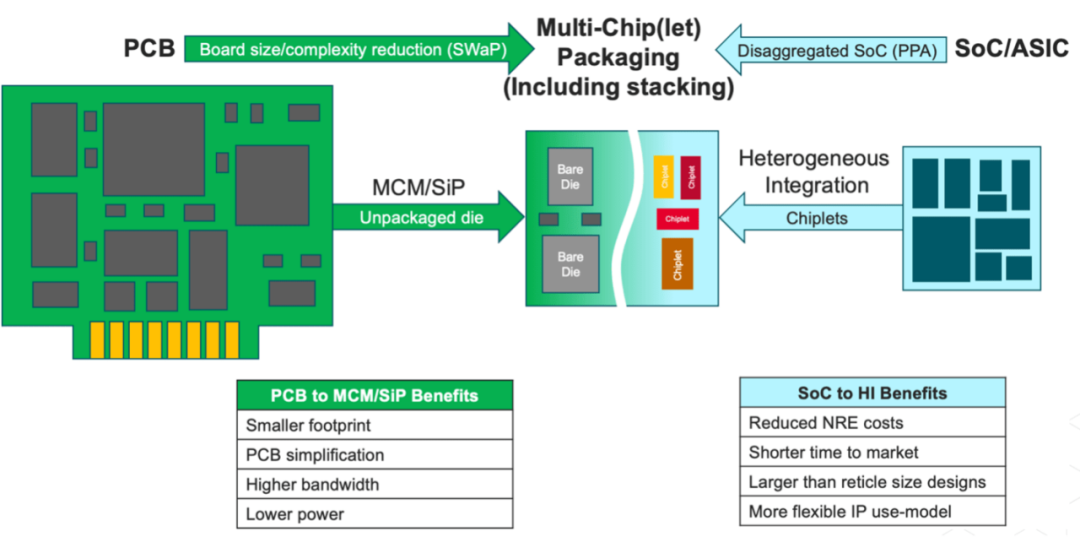

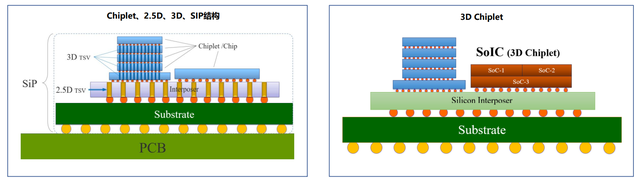

在探討Chiplet(小芯片)之前,摩爾定律是繞不開的話題。戈登·摩爾先生在1965 年提出了摩爾定律:每年單位面積內的晶體管數量會增加一倍,性能也會提升一倍。這意味著,在相同價格的基礎上,能獲得的晶體管數量翻倍。不過,摩爾先生在十年后的1975年,把定律的周期修正為24個月。至此,摩爾定律已經影響半導體行業有半個世紀。隨著集成電路技術的不斷演進,半導體行業發現摩爾定律在逐漸失效。上圖右上部分是英特爾x86 CPU 1970-2025年的演化歷史,可看出每顆芯片的晶體管數量持續增加(右上深藍色線條),但時

關鍵字:

Chiplet 芯片接口IP 摩爾定律失效

大家好,我是小胡。在前面的內容我們講國內六大CPU廠商的時候,發現了一個問題,就是國產CPU后續工藝迭代的問題。除了華為鯤鵬以外,其余五大CPU廠商目前主力芯片的制程工藝都在10nm以上,而六大廠商當中有四家被列入實體清單,鯤鵬920雖然是7nm工藝,但這兩年一直依靠庫存支撐,芯片供應鏈問題一直是國產CPU無法回避的問題。22年8月份之后,Chiplet技術,也就是芯粒技術在A股市場中熱度升高,我在看券商研報的時候發現,“超越摩爾定律”、“性能升級”、“彎道超車”、“產業突破”成為了研報當中的關鍵詞。今天

關鍵字:

Chiplet 摩爾定律

3dic chiplet介紹

您好,目前還沒有人創建詞條3dic chiplet!

歡迎您創建該詞條,闡述對3dic chiplet的理解,并與今后在此搜索3dic chiplet的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473