cadence reality 文章 最新資訊

Cadence 加強(qiáng)其 Tensilica Vision 和 AI 軟件合作伙伴生態(tài)

- 新加入的生態(tài)系統(tǒng)成員包括 Kudan 和 Visionary.ai,有助于快速部署高性能、高能效的基于 SLAM 和 AI ISP 的解決方案 中國上海,2023 年 4 月 12 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布?xì)g迎 Kudan 和 Visionary.ai 加入 Tensilica 軟件合作伙伴生態(tài)系統(tǒng),他們將為 Cadence? Tensilica? Vision DSP 和 AI 平臺帶來業(yè)界領(lǐng)先的同步與地圖構(gòu)建 (SLAM)和 AI 圖像

- 關(guān)鍵字: Cadence Tensilica Vision AI 軟件

Cadence 推出 Allegro X AI,旨在加速 PCB 設(shè)計(jì)流程,可將周轉(zhuǎn)時(shí)間縮短 10 倍以上

- 中國上海,2023 年 4 月 7 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Cadence? Allegro? X AI technology,這是 Cadence 新一代系統(tǒng)設(shè)計(jì)技術(shù),在性能和自動化方面實(shí)現(xiàn)了革命性的提升。這款 AI 新產(chǎn)品依托于 Allegro X Design Platform 平臺,可顯著節(jié)省 PCB 設(shè)計(jì)時(shí)間,與手動設(shè)計(jì)電路板相比,在不犧牲甚至有可能提高質(zhì)量的前提下,將布局布線(P&R)任務(wù)用時(shí)從數(shù)天縮短至幾分鐘。?

- 關(guān)鍵字: Cadence Allegro PCB

消息稱蘋果Reality Pro頭顯不需要iPhone配合使用

- IT之家 2 月 26 日消息,蘋果公司正在努力完善其 AR / VR 頭顯的第一個(gè)版本,預(yù)計(jì)將在 6 月發(fā)布。彭博社今天的一份新報(bào)告提供了一些關(guān)于 Reality Pro 頭顯的功能和局限性的細(xì)節(jié),包括是否需要 iPhone 配合使用。彭博社的馬克-古爾曼在其最新一期的 Power On 通訊中報(bào)道,最新測試版本的 Reality Pro 頭顯“將不需要 iPhone 來設(shè)置或使用”。這與過去的蘋果設(shè)備相比是一個(gè)很大的變化,如 Apple Watch,其最初需要 iPhone 來初始化設(shè)置。相反,Rea

- 關(guān)鍵字: 蘋果 Reality Pro 頭顯 iPhone

Cadence榮獲六項(xiàng)2022 TSMC OIP年度合作伙伴大獎(jiǎng)

- 內(nèi)容提要:·?????? Cadence 憑借關(guān)鍵的 EDA、云和 IP 創(chuàng)新榮獲 TSMC 大獎(jiǎng);·?????? Cadence 是 TSMC 3DFabric 聯(lián)盟的創(chuàng)始成員之一。?中國上海,2022年12月14日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其 EDA、IP 和云計(jì)算解決方案獲得了 TSMC 頒發(fā)的六項(xiàng) Open Innova

- 關(guān)鍵字: Cadence 2022 TSMC OIP

聯(lián)電與Cadence共同開發(fā)認(rèn)證的毫米波參考流程達(dá)成一次完成硅晶設(shè)計(jì)

- 聯(lián)華電子與全球電子設(shè)計(jì)創(chuàng)新領(lǐng)導(dǎo)廠商益華計(jì)算機(jī)(Cadence Design Systems, Inc.)于今(30)日宣布雙方合作經(jīng)認(rèn)證的毫米波參考流程,成功協(xié)助亞洲射頻IP設(shè)計(jì)的領(lǐng)導(dǎo)廠商聚睿電子(Gear Radio Electronics),在聯(lián)電28HPC+ 制程技術(shù)以及Cadence? 射頻(RF)解決方案的架構(gòu)下,達(dá)成低噪音放大器 (LNA) IC一次完成硅晶設(shè)計(jì)(first-pass silicon success) 的非凡成果。 經(jīng)驗(yàn)證的聯(lián)電28HPC+解決方案非常適合生產(chǎn)應(yīng)用于高

- 關(guān)鍵字: 聯(lián)電 Cadence 毫米波參考流程

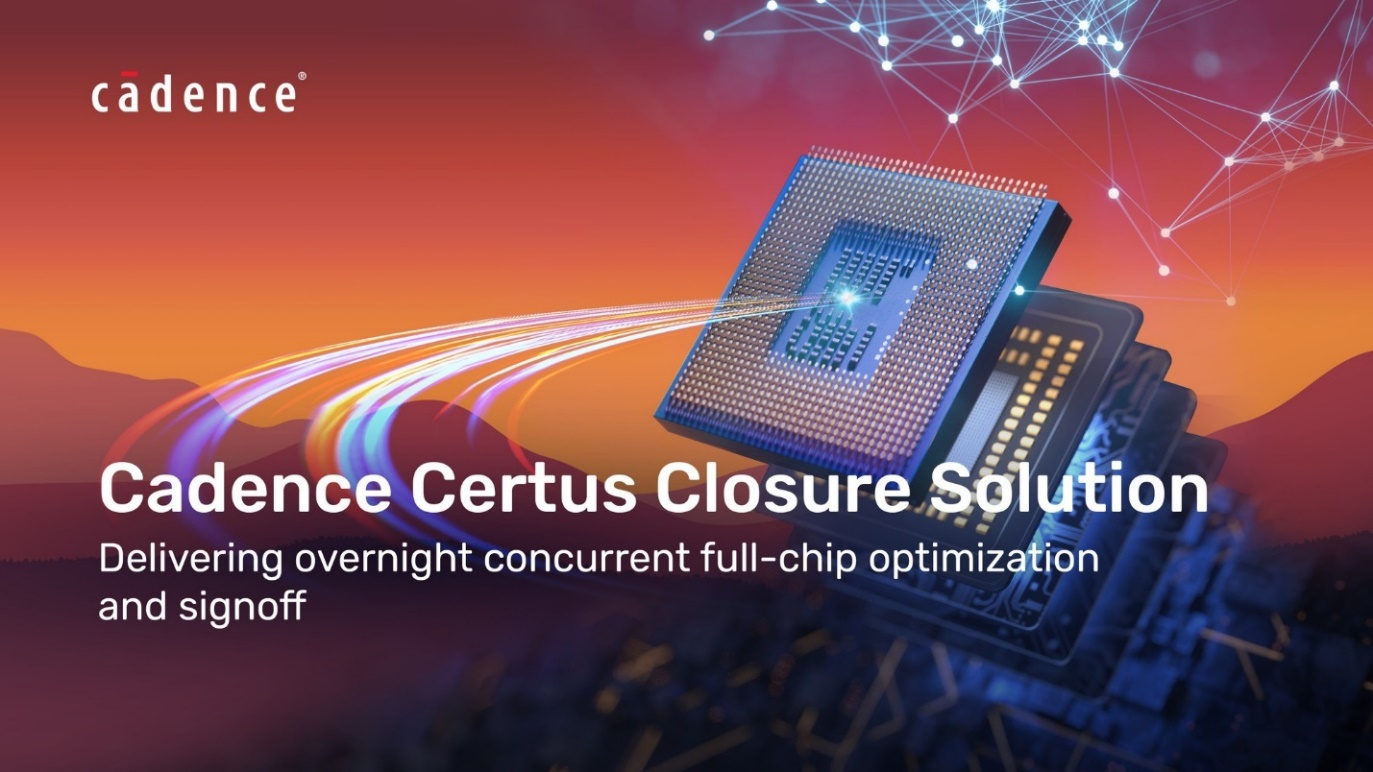

Cadence Certus新品亮相!助力全芯片并行優(yōu)化和簽核速度提高10倍

- 內(nèi)容提要:●? ?為客戶提供業(yè)內(nèi)首個(gè)具有大規(guī)模并行和分布式架構(gòu)的完全自動化環(huán)境;●? ?支持無限容量的設(shè)計(jì)優(yōu)化和簽核,周轉(zhuǎn)時(shí)間縮短至一夜,同時(shí)大幅降低設(shè)計(jì)功耗;●? ?支持云的解決方案,推動新興設(shè)計(jì)領(lǐng)域的發(fā)展,包括超大規(guī)模計(jì)算、5G 通信、移動、汽車和網(wǎng)絡(luò)。楷登電子(美國 Cadence 公司)近日宣布推出新的 Cadence??Certus??Closure Solution,以應(yīng)對不斷增長的芯片級設(shè)計(jì)尺寸和復(fù)雜性挑戰(zhàn)。Ca

- 關(guān)鍵字: Cadence 并行優(yōu)化 簽核速度

Cadence發(fā)布Verisium AI-Driven Verification Platform引領(lǐng)驗(yàn)證效率革命

- 楷登電子(美國 Cadence 公司)近日宣布,推出 Cadence? Verisium? Artificial Intelligence (AI)-Driven Verification Platform,整套應(yīng)用通過大數(shù)據(jù)和 JedAI Platform 來優(yōu)化驗(yàn)證負(fù)荷、提高覆蓋率并加速 bug 溯源。Verisium 平臺基于新的 Cadence Joint Enterprise Data AI (JedAI) Platform,并與 Cadence 驗(yàn)證引擎原生集成。隨著 SoC 復(fù)雜性不斷提高,

- 關(guān)鍵字: Cadence Verisium AI-Driven Verification Platform 驗(yàn)證

美媒:商標(biāo)申請文件顯示蘋果MR頭盔或名為Reality One

- 8月29日消息,最新商標(biāo)申請備案文件顯示,蘋果公司可能以Reality作為其混合現(xiàn)實(shí)(MR)設(shè)備的名字,這將是其多年來推出的首個(gè)全新產(chǎn)品類別。美國、歐盟、英國、加拿大、澳大利亞、新西蘭、沙特、哥斯達(dá)黎加和烏拉圭都收到了“Reality One”、“Reality Pro”和“Reality Processor”等商標(biāo)申請。盡管蘋果本身沒有參與,但這些申請都遵循了該公司過去使用過的模式,包括依賴之前聘請的律師事務(wù)所提供幫助。蘋果的MR頭盔預(yù)計(jì)將結(jié)合虛擬現(xiàn)實(shí)(VR)和增強(qiáng)現(xiàn)實(shí)(AR)技術(shù),使該公司與領(lǐng)先的VR

- 關(guān)鍵字: 蘋果 MR頭盔 Reality One

聯(lián)電與Cadence攜手22納米模擬與混合信號設(shè)計(jì)認(rèn)證

- 聯(lián)華電子與Cadence于今(8月24)日共同宣布,Cadence的模擬與混合信號(Analog/Mixed Signal, AMS)芯片設(shè)計(jì)流程獲得聯(lián)華電子22納米超低功耗 (22ULP)與22納米超低漏電(22ULL)制程認(rèn)證,此流程可優(yōu)化制程效率、縮短設(shè)計(jì)時(shí)間,加速5G、物聯(lián)網(wǎng)和顯示等應(yīng)用設(shè)計(jì)開發(fā),滿足日漸增高的市場需求。 聯(lián)電的22納米制程具有超低功耗和超低漏電的技術(shù)優(yōu)勢,可滿足在科技創(chuàng)新發(fā)展下,使用時(shí)間長、體積小、運(yùn)算強(qiáng)的應(yīng)用需求。經(jīng)聯(lián)電認(rèn)證的Cadence AMS設(shè)計(jì)流程,提供了整合

- 關(guān)鍵字: 聯(lián)電 Cadence 22納米 模擬與混合信號

瑞薩電子完成對Reality AI的收購

- 全球半導(dǎo)體解決方案供應(yīng)商瑞薩電子今日宣布,在獲得Reality AI股東及監(jiān)管機(jī)構(gòu)批準(zhǔn)后,于2022年7月19日完成對嵌入式AI解決方案優(yōu)秀供應(yīng)商——Reality Analytics, Inc.(Reality AI)的收購。 Reality AI總部位于美國馬里蘭州哥倫比亞市,為汽車、工業(yè)和消費(fèi)類產(chǎn)品中的高級非視覺傳感提供廣泛的嵌入式AI和微型機(jī)器學(xué)習(xí)(TinyML)解決方案。將Reality AI卓越的AI推理技術(shù)與瑞薩電子廣泛的MCU和MPU產(chǎn)品相結(jié)合,將實(shí)現(xiàn)機(jī)器學(xué)習(xí)和信號處理的無縫銜接

- 關(guān)鍵字: 瑞薩電子 Reality AI 收購

Cadence 通過面向 TSMC 先進(jìn)工藝的 PCIe 5.0 PHY 和控制器 IP 規(guī)范合規(guī)性認(rèn)證

- 楷登電子(美國 Cadence 公司)今日宣布,其面向 TSMC N7、N6 和 N5 工藝技術(shù) PCI Express?(PCIe?)5.0 規(guī)范的 PHY 和控制器 IP 在 4 月舉行的業(yè)界首次 PCIe 5.0 規(guī)范合規(guī)認(rèn)證活動中通過了 PCI-SIG? 的認(rèn)證測試。Cadence? 解決方案經(jīng)過充分測試,符合 PCIe 5.0 技術(shù)的 32GT/s 全速要求。該合規(guī)計(jì)劃為設(shè)計(jì)者提供測試程序,用以評估系統(tǒng)級芯片(SoC)設(shè)計(jì)的 PCIe 5.0 接口是否會按預(yù)期運(yùn)行。 面向 PCIe 5

- 關(guān)鍵字: Cadence TSMC PCIe 5.0

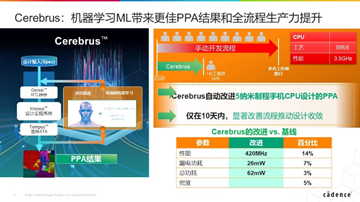

聯(lián)發(fā)科與瑞薩采用Cadence Cerebrus AI方案 優(yōu)化芯片PPA

- Cadence Design Systems, Inc.宣布,Cadence Cerebrus?智能芯片設(shè)計(jì)工具(Intelligent Chip Explorer) 獲得客戶采用于其全新量產(chǎn)計(jì)劃。此基于 Cadence Cerebrus 采用人工智能 (AI) 技術(shù)帶來自動化和擴(kuò)展數(shù)字芯片設(shè)計(jì)能力,能為客戶優(yōu)化功耗、效能和面積 (PPA),以及提高工程生產(chǎn)力。Cadence Cerebrus 運(yùn)用革命性的AI技術(shù),擁有獨(dú)特的強(qiáng)化學(xué)習(xí)引擎,可自動優(yōu)化軟件工具和芯片設(shè)計(jì)選項(xiàng),提供更好的 PPA進(jìn)而大幅減少工

- 關(guān)鍵字: 聯(lián)發(fā)科 瑞薩 Cadence Cerebrus AI 芯片PPA

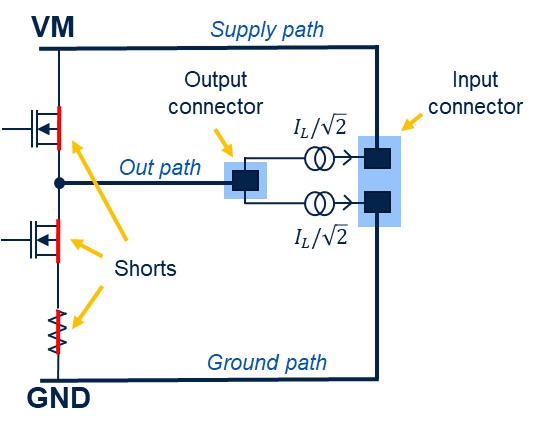

適用于電池供電設(shè)備的熱感知高功率高壓板

- 電池供電馬達(dá)控制方案為設(shè)計(jì)人員帶來多項(xiàng)挑戰(zhàn),例如,優(yōu)化印刷電路板熱效能至今仍十分棘手且耗時(shí);但現(xiàn)在,應(yīng)用設(shè)計(jì)人員可利用現(xiàn)代化電熱仿真器輕松縮短上市時(shí)間。如今,電池供電馬達(dá)驅(qū)動解決方案通常可用極低的工作電壓提供數(shù)百瓦的功率。在此類應(yīng)用中,為確保整個(gè)系統(tǒng)的效能和可靠性,必須正確管理馬達(dá)驅(qū)動設(shè)備的電流。事實(shí)上,馬達(dá)電流可能會超過數(shù)十安培,導(dǎo)致變流器內(nèi)部耗散功率提升。為變流器組件施加較高的功率將會導(dǎo)致運(yùn)作溫度升高,效能下降,如果超過最額定功率,甚至?xí)蝗煌V惯\(yùn)作。優(yōu)化熱效能同時(shí)縮小大小,是變流器設(shè)計(jì)過程中的重要一

- 關(guān)鍵字: 電池供電 熱感知 高功率高壓板 ST Cadence

當(dāng)人工智能遇到EDA,Cadence Cerebrus以機(jī)器學(xué)習(xí)提升EDA設(shè)計(jì)效能

- 隨著算力的不斷提升,人工智能的應(yīng)用逐漸滲透到各個(gè)行業(yè)。作為人工智能芯片最關(guān)鍵的開發(fā)工具EDA,是否也會得到人工智能應(yīng)用的助力從而更好地提升服務(wù)效率呢?答案自然是肯定的。隨著半導(dǎo)體芯片設(shè)計(jì)的復(fù)雜度不斷提升,以及芯片包含功能的日漸廣泛,EDA的設(shè)計(jì)過程越來越需要借助人工智能來盡可能避免一些常見的設(shè)計(jì)誤區(qū),并借助大數(shù)據(jù)的優(yōu)勢來實(shí)現(xiàn)局部電路設(shè)計(jì)的最優(yōu)化。在可以預(yù)見的未來,隨著人工智能技術(shù)的不斷引入,借助大數(shù)據(jù)和機(jī)器學(xué)習(xí)的優(yōu)勢,EDA軟件將可以提供更高效更強(qiáng)大的設(shè)計(jì)輔助功能。 近日,楷登電子(Cadenc

- 關(guān)鍵字: 人工智能 EDA Cadence Cerebrus

cadence reality介紹

您好,目前還沒有人創(chuàng)建詞條cadence reality!

歡迎您創(chuàng)建該詞條,闡述對cadence reality的理解,并與今后在此搜索cadence reality的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對cadence reality的理解,并與今后在此搜索cadence reality的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司