40納米500MHz DSP核心的時鐘設計與分析

4) 計算同級延時,

ESi,corner=Di,corner/ESDcorner

5) 理想上,每個接收端應可跨角點地擁有同等的級數,例如,對于接收端j,

ESj,corner1=ESj,corner2=…

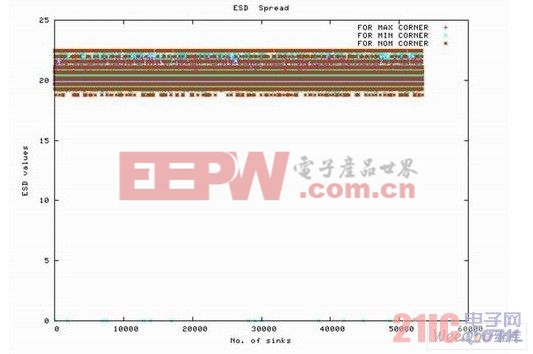

圖6和圖7所展示的例子是相同級數以及兩種實現方式的擴展。在圖6中,ESD擴展擁有從18到23的一種更好分布。在圖7中,微捷碼自帶CTS結果顯示了從27到37的一種分布。

圖7使用微捷碼自帶CTS的ESD擴展

新時鐘設計方法已經實施于40納米DSP核心。事實證明,使用這種方法的CTS單元門數要比使用微捷碼自帶CTS工具的少了17%。魯棒性低偏斜時鐘樹分布現已成功實現。實驗結果顯示,新設計方法在降低保持緩沖器門數方面可起到很好效果。同時這種設計方法還可用于H-tree時鐘結構。未來工作中,我們還將部署更多分析來改善功耗。

評論