高性能片內集成CMOS線性穩壓器設計

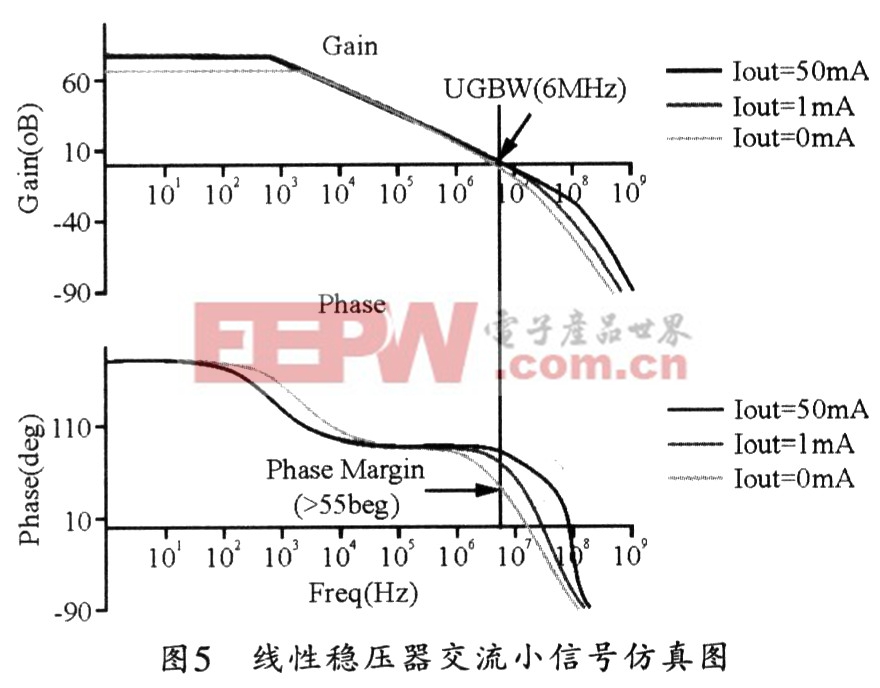

設計可從輸出壓降VDROP和最大負載電流開始,并由此定義功率管的參數,再定義微分器參數,然后確定差分運放的參數,最后選擇補償電容Cf3。圖5給出了三種負載條件下的電路Spice仿真結果,在溫度-25度到75度范圍內,無偏外電容線性穩壓器的環路增益帶寬大于1MHz條件下,其相位裕度可超過50度。而對于較小的負載電容.環路的單位增益帶寬與電路的穩定性都將得到提高。本文引用地址:http://cqxgywz.com/article/181155.htm

3 仿真結果分析

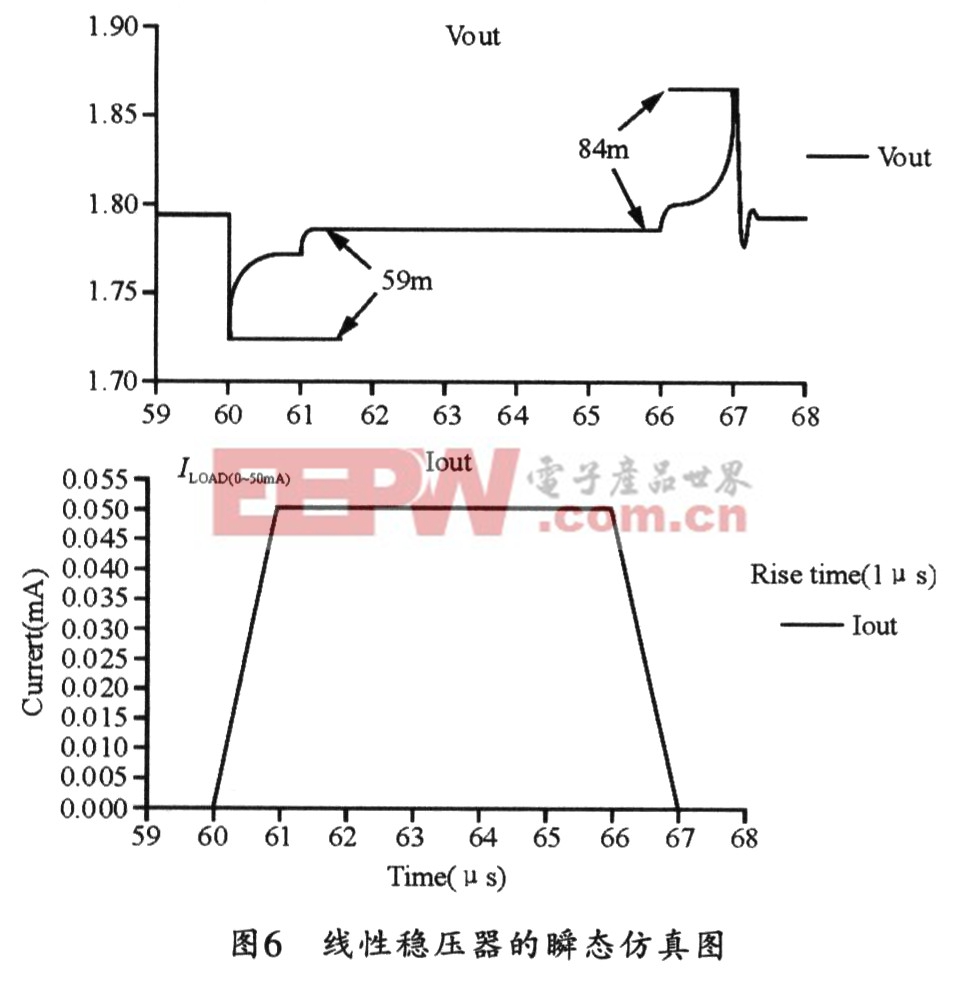

整個LDO的設計可采用SMIC 0.13μm CMOS工藝實現。面積為0.22 mm2,靜態電流為300μA,片內電容為100 pF,版圖的大部分面積為片內電容和功率管。在負載瞬態電流從0~50 mA變化,且電流上升下降時間為1 μs的條件下,就會出現圖6所示的仿真結果。

由圖6可見,當負載電流從0~50 mA瞬態變化時,輸出電壓紋波分別為84 mV和59mV,鎖定時間大約為4μs。當負載電流從10~50 mA瞬態變化時,輸出紋波小于20 mV。穩壓器的開啟時間小于1O μs。而在負載為電流為10 mA,電源上加輸入正弦信號時,其線性穩壓器的電源抑制比(PSRR)為100 kHz頻率下為-50 dB,在1 kHz頻率下為-53 dB。

4 結束語

仿真結果表明,本文所提的無片外電容線性穩壓器在犧牲了一部分靜態功耗的情況下,可在同類產品中表現出良好的瞬態響應和穩定性,且其片內電容可以隨著負載電容的增大而減小。因此,在保證環路穩定性的條件下,負載電容可以在一個較大范圍內變化。本文所提出的無片外電容線性穩壓器可以簡化和降低測試板和封裝的設計與成本。故可廣泛應用于片上系統的設計。

評論