imec觀點:微影圖形化技術的創新與挑戰

此篇訪談中,比利時微電子研究中心(imec)先進圖形化制程與材料研究計劃的高級研發SVP Steven Scheer以近期及長期發展的觀點,聚焦圖形化技術所面臨的研發挑戰與創新。本篇訪談內容,主要講述這些技術成果的背后動力,包含高數值孔徑(high NA)極紫外光(EUV)微影技術的進展、新興內存與邏輯組件的概念興起,以及減少芯片制造對環境影響的需求。

怎么看待微影圖形化這塊領域在未來2年的發展?

Steven Scheer表示:「2019年,極紫外光(EUV)微影技術在先進邏輯晶圓廠進入量產,如今動態隨機存取內存(DRAM)廠商也對采用EUV制程越來越感興趣。這一切都要歸功于艾司摩爾(ASML)的傾心傾力與堅持研發,有了他們的助力,這項技術才能取得超乎意料的重大突破。新一波革命是引進高數值孔徑(0.55NA)的EUV微影技術,把光學成像的半間距(half pitch)縮小至8nm。

新一波革命是引進高數值孔徑(0.55NA)的EUV微影技術,把光學成像的半間距縮小至8nm。

為了推動業界采用高數值孔徑的EUV微影技術,imec與艾司摩爾正在連手創建高數值孔徑極紫外光實驗室(High NA EUV Lab),用來滿足High-NA芯片制造商在早期開發階段的需求。同時,我們也在更廣泛的生態系與圖形化設備與材料廠商合作,藉此開放High NA實驗室的資源,并籌備EUV光阻劑材料、涂料底層、干式蝕刻、光罩、分辨率增益技術(resoulution enhancement technique)與量測技術。」

引進High NA技術有何優先考慮?

「High NA工具的可用性顯然是首要之務。在模塊與光學組件的整合技術方面,艾司摩爾與蔡司目前取得亮眼進展。雖說在制程方面,為了引進低數值孔徑(low NA)的EUV技術,創新的解決方案至今仍在持續開發,但未來還需更多的技術革命,才能有效導入High NA EUV技術。除了High NA工具,EUV光阻劑一直是imec與生態系伙伴的研發重心之一。High NA EUV微影技術的進展將能在較短的焦點深度(depth of focus)下,進一步提升光學分辨率并縮小組件的特征尺寸。這自然會導致光阻薄膜的厚度下降,因此需要利用新興光阻劑與涂料,以優化蝕刻階段的EUV吸收與圖形轉移。

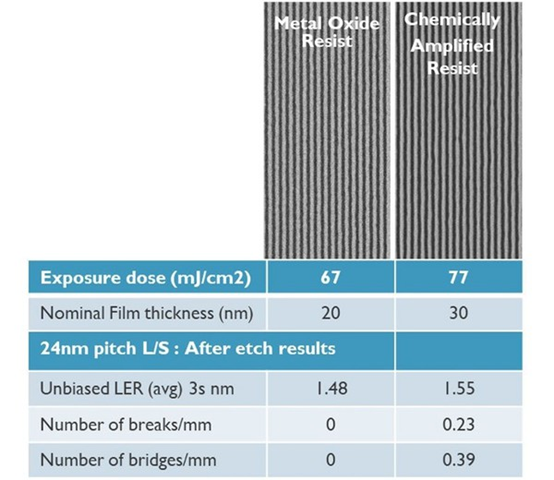

此外,我們還要持續推動改良隨機性粗糙度的問題,甚至是我們幾年前發現采用EUV進行圖形化所面臨的光阻劑缺陷問題。就光阻劑的圖形化性能來說,過去都以分辨率(resolution)、線邊緣粗糙度(LER)或局部線寬均勻度(LCDU)以及敏感度(sensitivity)為性能指針,三者合稱為RLS參數。

但現在考慮到隨機性的重要,因此在早期研發階段新增了第四個圖形化性能指針,也就是缺陷(failure),藉此反映制程受隨機性影響的操作范圍限制。針對由光阻系統誘發的隨機缺陷,我們相信勢必會有解決方案能減緩這些問題,同時放寬制程的操作范圍,并降低光阻劑量,我們也計劃攜手伙伴在High NA實驗室一同展示這些新技術。

降低特征尺寸與光阻薄膜厚度也會影響量測技術。除了轉印性能,大幅降低光學成像尺寸有可能會拉低準度(accuracy)與精度(precision),進而帶給量測與檢測性能負面影響。

如何協助應對EUV光阻劑的挑戰?

「針對傳統多成分混合光阻系統的化學隨機性問題,也就是除了散射噪聲以外的隨機現象,我們正在研發新興材料。例如,含金屬光阻劑或單成分光阻劑。imec持續協助材料供貨商進行概念開發及像是污染風險和制程整合技術等關鍵問題評估。

新型High NA EUV光阻系統的研發工作不能各自為政,為了達到最佳成效,就必須在涂料工程、新型硬罩與高選擇性蝕刻制程方面進行協同優化。面對這項挑戰,imec近期開發了用來配對光阻劑與涂料特性的全新工具箱。經過材料篩選、表面能匹配研究、材料物理特性分析與接口工程,采用旋轉涂布或沉積制程的涂料底層(underlayer)薄膜就能與光阻劑一起曝光,形成更微距的EUV圖形,并優化在LER、敏感度與缺陷度(defectivity)方面的表現。

除此之外,為了加速材料開發,我們建立了圖形化材料特性分析的基礎結構,稱之為Attolab的工具箱,用以解析光阻劑與涂料底層在EUV曝光時的行為表現。現在研究薄膜與堆棧的吸收系數與層解析(layer-resolved)結構特性時,就能搭配輻射測量及反射測量,這些技術都開放給Attolab研究伙伴使用。

圖一 : 24奈米線寬(line)與間距(space):金屬氧化物阻劑(metal-oxid resist;MOR)與化學放大型阻劑(chemically amplified resist;CAR)的圖形化技術開發。MOR所需的劑量較低,且在厚度較薄的情況下,LER與缺陷表現仍較佳。

為了推動新一代微影技術,imec還探索了哪些發展方向?

「現階段正在開發幾項新型光罩技術。為了減少EUV曝光劑的用量,目前鎖定具備低折射率吸收層的光罩技術展開積極研究,因為這些光罩能在使用低曝光劑量的情況下,產生對比度或正規化影像對數斜率(normalized image log slope)較高的空間強度輪廓。

imec也考慮到晶圓圖形化的隨機性誤差與光罩的3D成像效果,也就是光罩3D拓撲空間影像的失真問題。晶圓上的隨機缺陷成因很多,光罩的變異性(variability)就是其一。為了解決這項問題,我們研究有哪些類型的光罩變異性(包含不同粗糙度)較易導致晶圓上的隨機缺陷,以提出光罩及空白光罩的新版規格為目標。

此外,High NA EUV曝光機將會采用變形鏡片,這使得x軸與y軸的放大倍率并不一致。該變形現象代表著晶圓勢必需要進行圖形接合,以此取得與其它傳統光刻技術相同的曝光區域面積。晶圓圖形接合較著重在光罩曝光區域邊緣的質量,以及可能用來減緩邊緣缺陷的方案。

深入了解光罩與EUV光學的交互作用越來越重要,有鑒于此,imec整合了完整的光罩研發生態系統。透過與光罩及空白光罩廠商合作,我們協助光罩創新(像是新興吸收劑)產業化,以及探索光罩的復雜特性(像是變異性或圖形接合),這些都在imec與艾司摩爾共同建立的High NA EUV實驗室執行并經過模擬。

這些問題都不是引進High NA EUV技術的主要障礙。但為了以無阻、快速且高成本效益的方式引進最高效的High NA EUV技術,積極應對這些挑戰,并提供生態系統內的關鍵廠商一套有效的合作平臺,至關重要。imec與艾司摩爾當初以世界首臺High NA曝光機為中心而創立High NA EUV實驗室,主要目標就是推動業界盡速導入High NA EUV微影技術并擴大其產能。」

圖形化領域在未來2~5年會受到什么其它發展影響?

「除了EUV微影技術的創新,邏輯及內存的新興組件概念越來越常采用三維的結構設計,這也會帶給特殊圖形化技術一些新的契機。

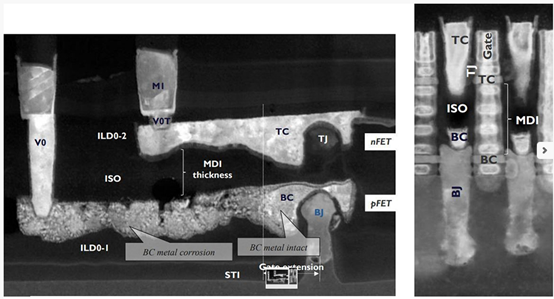

互補式場效晶體管(CFET)是繼閘極環繞(GAA)奈米片之后的新一代組件架構,其運用了在FET信道上堆棧另一個FET組件的概念。制造CFET組件需要具備高深寬比的圖形化步驟,才能制出主動組件、閘極、源極/汲極凹槽蝕刻,以及中段制程的M0A層接點。另外,大量的材料蝕刻也將必不可少,像是金屬或介電材料等。

在減少CFET制程復雜度方面,由下而上的沉積設計或區域選擇性沉積(area selective deposition)等創新方法能發揮重要作用。接著,CFET組件可能會與晶背供電網絡(BSPDN)整合,使得CFET標準組件從5軌微縮至4軌設計。這種新型布線方法需要高深寬比通孔的蝕刻技術及自對準的圖形化技術,且對閘極側壁呈現良好的蝕刻選擇性。

邏輯及內存的新興組件概念越來越常采用三維的結構設計,這也帶給特殊圖形化技術新的契機。

在內存方面,動態隨機存取內存(DRAM)目前是以扁深構形的電容作為內存單元。為了增加內存密度而微縮間距時,電容的橫向關鍵尺寸(CD)會持續縮小,且其構形必須越來越高,才能維持相同的電容。這不僅會帶來制造問題和產量損失,我們更預期2D DRAM將會觸碰材料的基本底線。

為了克服這些問題,不同的3D DRAM制程現已納入考慮,模塊相關的主要挑戰也在設法解決。可以想見半導體氧化物等新型材料將會獲得采用,另以高深寬比蝕刻及橫向凹槽蝕刻等數道步驟作為輔助,但這些在許多方面仍面臨了挑戰。其次,就技術難度而言,以襯墊層、介電材料及金屬填補縱向孔洞及橫向凹槽預計會至少與3D NAND閃存技術相當,極具挑戰。」

圖二 : imec先進圖形化制程與材料研究計劃的高級研發副主任Steven Scheer。(source:imec)

imec團隊在研究制程與材料時,如何協助推動永續制造?

「就現況預估,芯片制造約占了0.1%的全球碳排放。雖然如此,由于先進制程越來越復雜,制造邏輯芯片所衍生的二氧化碳排放估計會在未來10年翻倍。同時,晶圓的總產量預計也會每年增加約8%。若不采取行動,芯片制造產生的碳排量將在未來10年成長4倍。根據巴黎協議,所有產業都該在每10年減少一半的碳排放。換言之,要是我們「放手不搏」,芯片產業距離減排目標將會相差8倍。

因此,imec研究的其中一項重點就是永續性。我們已經發起永續半導體技術與系統(Sustainable Semiconductor Technologies and Systems)研究計劃,集結芯片制造供應鏈,以凈零碳排為共同目標。為了量化一般晶圓廠所帶來的環境影響,我們也在建立名叫imec.netzero模擬平臺的虛擬晶圓廠。藉由與設備與材料廠商建立合作,目前已開發的模塊仍在研究測量基準與進行驗證。

在2023年國際光電工程學會(SPIE)先進微影成形技術會議(Advanced Lithography and Patterning Conference)上,imec展示了先進芯片圖形化制程對碳排放影響的量化評估方案。在imec的實體晶圓廠,高影響力領域也已確認并鎖定為解決方案的目標。例如,減少含氟的蝕刻氣體用量、減少用水量、回收稀有材料、回收氫氣及降低微影制程的化學劑量。

在開發新一代技術的同時,還要面對其帶來的環境影響,似乎是令人卻步的艱難任務。的確沒錯,但我們做得到。芯片產業以創意及創新聞名,而我們現在只需加上一條開發要件:減少環境影響。」

(Steven Scheer為imec先進圖形化制程與材料研究計劃的高級研發副主任;編譯/吳雅婷)

評論