cadence 文章 最新資訊

Cadence榮獲六項2022 TSMC OIP年度合作伙伴大獎

- 內容提要:·?????? Cadence 憑借關鍵的 EDA、云和 IP 創(chuàng)新榮獲 TSMC 大獎;·?????? Cadence 是 TSMC 3DFabric 聯(lián)盟的創(chuàng)始成員之一。?中國上海,2022年12月14日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其 EDA、IP 和云計算解決方案獲得了 TSMC 頒發(fā)的六項 Open Innova

- 關鍵字: Cadence 2022 TSMC OIP

聯(lián)電與Cadence共同開發(fā)認證的毫米波參考流程達成一次完成硅晶設計

- 聯(lián)華電子與全球電子設計創(chuàng)新領導廠商益華計算機(Cadence Design Systems, Inc.)于今(30)日宣布雙方合作經(jīng)認證的毫米波參考流程,成功協(xié)助亞洲射頻IP設計的領導廠商聚睿電子(Gear Radio Electronics),在聯(lián)電28HPC+ 制程技術以及Cadence? 射頻(RF)解決方案的架構下,達成低噪音放大器 (LNA) IC一次完成硅晶設計(first-pass silicon success) 的非凡成果。 經(jīng)驗證的聯(lián)電28HPC+解決方案非常適合生產應用于高

- 關鍵字: 聯(lián)電 Cadence 毫米波參考流程

Cadence發(fā)布Verisium AI-Driven Verification Platform引領驗證效率革命

- 楷登電子(美國 Cadence 公司)近日宣布,推出 Cadence? Verisium? Artificial Intelligence (AI)-Driven Verification Platform,整套應用通過大數(shù)據(jù)和 JedAI Platform 來優(yōu)化驗證負荷、提高覆蓋率并加速 bug 溯源。Verisium 平臺基于新的 Cadence Joint Enterprise Data AI (JedAI) Platform,并與 Cadence 驗證引擎原生集成。隨著 SoC 復雜性不斷提高,

- 關鍵字: Cadence Verisium AI-Driven Verification Platform 驗證

聯(lián)電與Cadence攜手22納米模擬與混合信號設計認證

- 聯(lián)華電子與Cadence于今(8月24)日共同宣布,Cadence的模擬與混合信號(Analog/Mixed Signal, AMS)芯片設計流程獲得聯(lián)華電子22納米超低功耗 (22ULP)與22納米超低漏電(22ULL)制程認證,此流程可優(yōu)化制程效率、縮短設計時間,加速5G、物聯(lián)網(wǎng)和顯示等應用設計開發(fā),滿足日漸增高的市場需求。 聯(lián)電的22納米制程具有超低功耗和超低漏電的技術優(yōu)勢,可滿足在科技創(chuàng)新發(fā)展下,使用時間長、體積小、運算強的應用需求。經(jīng)聯(lián)電認證的Cadence AMS設計流程,提供了整合

- 關鍵字: 聯(lián)電 Cadence 22納米 模擬與混合信號

Cadence 通過面向 TSMC 先進工藝的 PCIe 5.0 PHY 和控制器 IP 規(guī)范合規(guī)性認證

- 楷登電子(美國 Cadence 公司)今日宣布,其面向 TSMC N7、N6 和 N5 工藝技術 PCI Express?(PCIe?)5.0 規(guī)范的 PHY 和控制器 IP 在 4 月舉行的業(yè)界首次 PCIe 5.0 規(guī)范合規(guī)認證活動中通過了 PCI-SIG? 的認證測試。Cadence? 解決方案經(jīng)過充分測試,符合 PCIe 5.0 技術的 32GT/s 全速要求。該合規(guī)計劃為設計者提供測試程序,用以評估系統(tǒng)級芯片(SoC)設計的 PCIe 5.0 接口是否會按預期運行。 面向 PCIe 5

- 關鍵字: Cadence TSMC PCIe 5.0

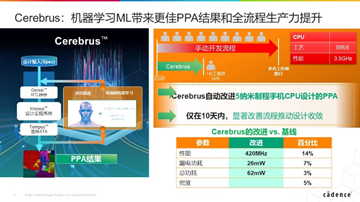

聯(lián)發(fā)科與瑞薩采用Cadence Cerebrus AI方案 優(yōu)化芯片PPA

- Cadence Design Systems, Inc.宣布,Cadence Cerebrus?智能芯片設計工具(Intelligent Chip Explorer) 獲得客戶采用于其全新量產計劃。此基于 Cadence Cerebrus 采用人工智能 (AI) 技術帶來自動化和擴展數(shù)字芯片設計能力,能為客戶優(yōu)化功耗、效能和面積 (PPA),以及提高工程生產力。Cadence Cerebrus 運用革命性的AI技術,擁有獨特的強化學習引擎,可自動優(yōu)化軟件工具和芯片設計選項,提供更好的 PPA進而大幅減少工

- 關鍵字: 聯(lián)發(fā)科 瑞薩 Cadence Cerebrus AI 芯片PPA

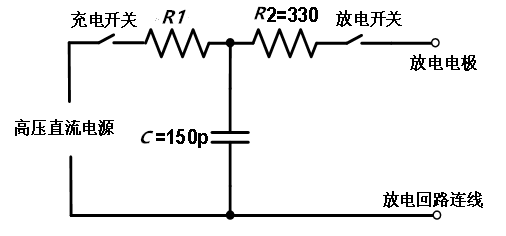

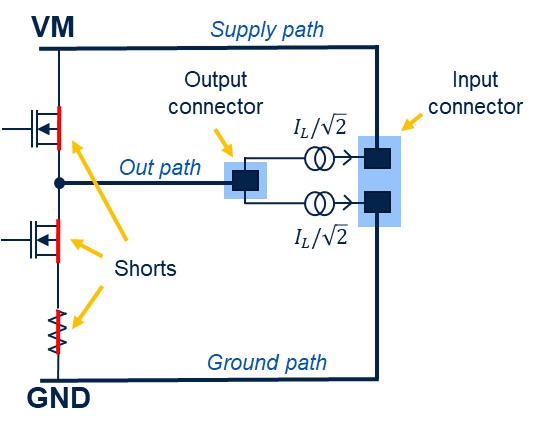

適用于電池供電設備的熱感知高功率高壓板

- 電池供電馬達控制方案為設計人員帶來多項挑戰(zhàn),例如,優(yōu)化印刷電路板熱效能至今仍十分棘手且耗時;但現(xiàn)在,應用設計人員可利用現(xiàn)代化電熱仿真器輕松縮短上市時間。如今,電池供電馬達驅動解決方案通常可用極低的工作電壓提供數(shù)百瓦的功率。在此類應用中,為確保整個系統(tǒng)的效能和可靠性,必須正確管理馬達驅動設備的電流。事實上,馬達電流可能會超過數(shù)十安培,導致變流器內部耗散功率提升。為變流器組件施加較高的功率將會導致運作溫度升高,效能下降,如果超過最額定功率,甚至會突然停止運作。優(yōu)化熱效能同時縮小大小,是變流器設計過程中的重要一

- 關鍵字: 電池供電 熱感知 高功率高壓板 ST Cadence

當人工智能遇到EDA,Cadence Cerebrus以機器學習提升EDA設計效能

- 隨著算力的不斷提升,人工智能的應用逐漸滲透到各個行業(yè)。作為人工智能芯片最關鍵的開發(fā)工具EDA,是否也會得到人工智能應用的助力從而更好地提升服務效率呢?答案自然是肯定的。隨著半導體芯片設計的復雜度不斷提升,以及芯片包含功能的日漸廣泛,EDA的設計過程越來越需要借助人工智能來盡可能避免一些常見的設計誤區(qū),并借助大數(shù)據(jù)的優(yōu)勢來實現(xiàn)局部電路設計的最優(yōu)化。在可以預見的未來,隨著人工智能技術的不斷引入,借助大數(shù)據(jù)和機器學習的優(yōu)勢,EDA軟件將可以提供更高效更強大的設計輔助功能。 近日,楷登電子(Cadenc

- 關鍵字: 人工智能 EDA Cadence Cerebrus

大幅縮減設計進程 Cadence新設備為硬件仿真驗證提速

- 當前隨著國內IC設計產業(yè)越來越受關注,短時間內涌現(xiàn)出海量的IC設計初創(chuàng)企業(yè),對這些初創(chuàng)或者正在快速成長的IC設計企業(yè)來說,如何盡可能縮短設計進程,加速設計上市時間是一個不可回避的關鍵點。作為當下幾乎已經(jīng)占據(jù)IC設計近60%工作量的仿真與驗證環(huán)節(jié),如果能夠借助先進的工具大幅縮短這個過程所需的時間,那么將為諸多IC設計企業(yè)的產品成功增添重要的砝碼。 為了更好地提升IC設計客戶的仿真與驗證效率,三大EDA公司不斷更新各自的仿真驗證工具,希望盡可能將該環(huán)節(jié)的時間大幅壓縮,其中Cadence選擇推出下一代

- 關鍵字: Cadence Palladium Z2 Protium X2 仿真驗證

Cadence推出新一代電路仿真器FastSPICE 效能高達3倍

- Cadence 宣布全新的Cadence Spectre FX 仿真器(Simulator),此新一代的FastSPICE電路仿真器能夠有效驗證內存和大規(guī)模系統(tǒng)單芯片(SoC)設計。Spectre FX 仿真器中具創(chuàng)新和可擴展性的FastSPICE架構,可為客戶提供高達3倍的效能。當今復雜的內存和SoC設計需要高精度和快速模擬效能,以確保按預期運作并滿足芯片規(guī)格。 此外,在芯片驗證過程中,布局后寄生效應變得越來越重要,尤其是對于先進制程設計而言,要考慮布局對芯片功能的影響。 FastSPICE求解器可在S

- 關鍵字: Cadence 電路仿真器 FastSPICE

云端部署引領IC設計邁向全自動化

- 隨著科技應用走向智能化、客制化,系統(tǒng)復雜度明顯增長,IC設計業(yè)者要搶占車用、通訊或物聯(lián)網(wǎng)等熱門市場,以強大運算力實現(xiàn)快速驗證與設計已不足夠,部署彈性和整合資源將成為開發(fā)的關鍵考慮,云端部署會是重要的一步棋。通訊、車用和物聯(lián)網(wǎng)是未來IC應用的主要場域,尤其隨著持續(xù)開發(fā)人工智能應用,以及擴大部署5G、Wi-Fi 6等新一代網(wǎng)絡技術,這些頗具潛力的應用展現(xiàn)了強勁成長。根據(jù)市調機構IC Insights上(6)月公布的研究顯示,消費性及通訊IC類仍居IC市場最高市占率,至2024年預計將達35.5%,在近20年來

- 關鍵字: Cadence 臺積電 EDA IC設計

cadence介紹

EDA仿真軟件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的電子設計技術(Electronic Design Technologies)、程序方案服務和設計服務供應商。其解決方案旨在提升和監(jiān)控半導 [ 查看詳細 ]

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司