chiplet phy designer 文章 最新資訊

(2023.10.7)半導(dǎo)體周要聞-莫大康

- 半導(dǎo)體周要聞2023.9.28-2023.10.61. 英特爾決戰(zhàn)2nm,4年追趕5代制程,與臺積電維持競合關(guān)系明年底,英特爾將推進(jìn)至18A制程,挑戰(zhàn)臺積電2nm制程,并將用于2025年推出的服務(wù)器處理器產(chǎn)品上。英特爾認(rèn)為,屆時將用比超微更佳的制程奪回市場。臺積電則預(yù)計于2025年量產(chǎn)2nm制程芯片。基辛格宣告英特爾下一代制程20A將在明年上半年推出。A代表埃米,一埃米是10分之1nm,20A代表的即是2nm制程。由于電晶體的體積極小,因此,英特爾將改采用GAA(閘極全環(huán)電晶體)技術(shù)設(shè)計的新型電晶體「Ri

- 關(guān)鍵字: 臺積電 chiplet 英特爾

Valens符合MIPI A-PHY標(biāo)準(zhǔn)的VA7000芯片組賦能應(yīng)用于高級駕駛輔助系統(tǒng)的雷達(dá)連接技術(shù)的轉(zhuǎn)型

- 家在音視頻領(lǐng)域和汽車市場領(lǐng)先的高性能連接方案供應(yīng)商Valens Semiconductor(以下簡稱Valens)宣布將在2023年布魯塞爾汽車傳感技術(shù)展覽會上展示其汽車解決方案以及其技術(shù)如何改革高速傳感器連接方法。屆時,Valens將攜手Smart Radar System(SRS)聯(lián)合展示一項專注于先進(jìn)駕駛輔助系統(tǒng)的新一代集中式雷達(dá)和傳感器融合功能,其中Valens VA7000芯片搭載于SRS的軟件定義成像雷達(dá)中。VA7000芯片這一組合解決方案為汽車行業(yè)帶來了顯著優(yōu)勢,例如能夠使用體積更小的雷達(dá)和

- 關(guān)鍵字: Valens MIPI A-PHY 高級駕駛輔助系統(tǒng) 雷達(dá)連接技術(shù)

Achronix幫助用戶基于Speedcore eFPGA IP來構(gòu)建Chiplet

- 高性能FPGA芯片和嵌入式FPGA IP(eFPGA?IP)領(lǐng)域內(nèi)的先鋒企業(yè)Achronix半導(dǎo)體公司日前宣布:為幫助用戶利用先進(jìn)的Speedcore eFPGA IP來構(gòu)建先進(jìn)的chiplet解決方案,公司開通專用網(wǎng)頁介紹相關(guān)技術(shù),以幫助用戶快速構(gòu)建新一代高靈活性、高性價比的chiplet產(chǎn)品, chiplet設(shè)計和開發(fā)人員可以透過該公司網(wǎng)站獲得有關(guān)Speedcore eFPGA IP的全面支持。中國客戶亦可以通過Achronix在中國的服務(wù)團(tuán)隊得到同樣的支持。Speedcore??

- 關(guān)鍵字: Achronix FPGA Chiplet

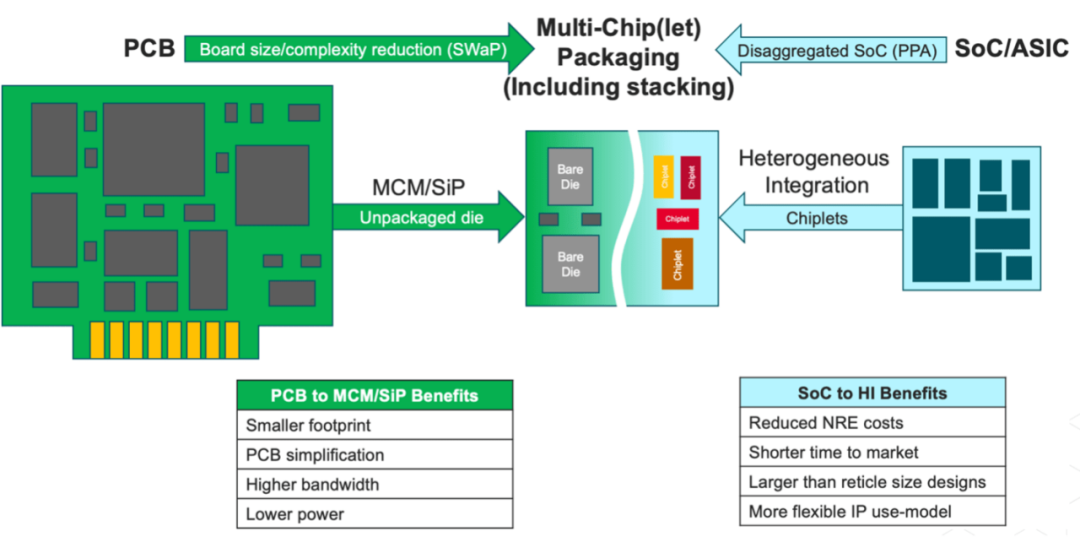

AI熱潮下,芯片制造商將芯片堆疊起來,就像搭積木

- 7月11日消息,人工智能熱潮推動芯片制造商加速堆疊芯片設(shè)計,就像高科技的樂高積木一樣。業(yè)內(nèi)高管稱,這種所謂的Chiplet(芯粒)技術(shù)可以更輕松地設(shè)計出更強(qiáng)大的芯片,它被認(rèn)為是集成電路問世60多年以來最重要的突破之一。IBM研究主管達(dá)里奧·吉爾(Darío Gil)在接受采訪時表示:“封裝和Chiplet技術(shù)是半導(dǎo)體的未來重要組成部分。”“相比于從零開始設(shè)計一款大型芯片,這種技術(shù)更加強(qiáng)大。”去年,AMD、英特爾、微軟、高通、三星電子和臺積電等科技巨頭組成了一個聯(lián)盟,旨在制定Chiplet設(shè)計標(biāo)準(zhǔn)。英偉達(dá),

- 關(guān)鍵字: AI 芯片制造 Chiplet 臺積電 人工智能

泰瑞達(dá)亮相SEMICON China:解讀異構(gòu)集成和Chiplet時代下,測試行業(yè)的機(jī)遇與挑戰(zhàn)

- 2023年7月3日,中國 北京訊 —— 全球先進(jìn)的自動測試設(shè)備供應(yīng)商泰瑞達(dá)(NASDAQ:TER)宣布,受邀出席了SEMICON China 2023同期舉辦的“先進(jìn)封裝論壇 - 異構(gòu)集成”活動。在活動中,泰瑞達(dá)Complex SOC事業(yè)部亞太區(qū)總經(jīng)理張震宇發(fā)表題為《異構(gòu)集成和Chiplet時代下,芯片測試行業(yè)的機(jī)遇與挑戰(zhàn)》的精彩演講,生動介紹泰瑞達(dá)對于先進(jìn)封裝,在質(zhì)量和成本之間找到平衡和最優(yōu)方案的經(jīng)驗和見解。 SEMICON China是中國最重要的半導(dǎo)體行業(yè)盛事之一,見證中國半導(dǎo)體制造業(yè)的茁

- 關(guān)鍵字: 泰瑞達(dá) SEMICON China 異構(gòu)集成 Chiplet

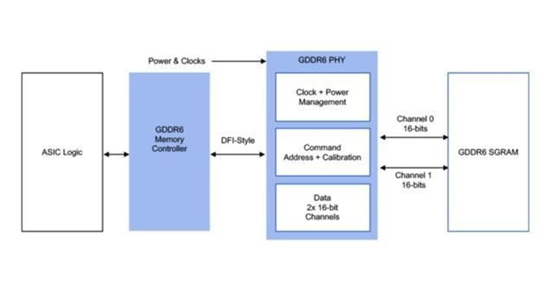

Rambus高速GDDR6 PHY打通AI應(yīng)用的數(shù)據(jù)瓶頸

- 幾年前當(dāng)AI剛開始流行之時,很多人預(yù)測AI應(yīng)用最大的瓶頸將是存儲器的讀取和寫入速度,這會嚴(yán)重影響訓(xùn)練和推斷的效率,以及做出相應(yīng)反饋的速度。特別是2023年以來,以ChatGPT為代表的生成式AI讓人們看到了智能世界的無限可能,而如何有效地采集、存儲、傳輸、處理數(shù)據(jù)和模型則成為實現(xiàn)高質(zhì)量AI的關(guān)鍵,這就需要高速傳輸技術(shù)的革新。 無論是云端AI訓(xùn)練還是向網(wǎng)絡(luò)邊緣轉(zhuǎn)移的AI推理,都需要高帶寬、低時延的內(nèi)存。鑒于GPU已經(jīng)成為目前人工智能訓(xùn)練和推理中的核心處理單元,邁向高性能GDDR6內(nèi)存接口已是大勢所趨。近日,

- 關(guān)鍵字: Rambus 高速GDDR6 PHY AI

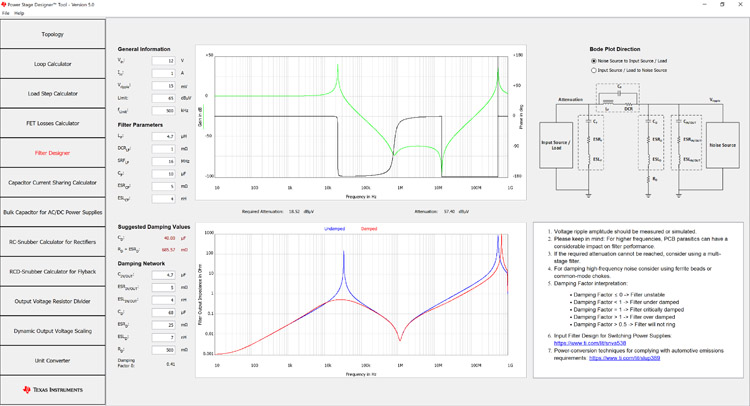

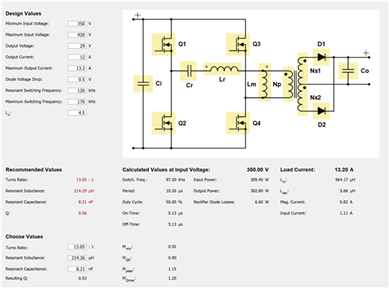

POWERSTAGE-DESIGNER 適用于常用開關(guān)模式電源的 Power Stage Designer? 軟件工具

- 概述Power Stage Designer 是一款基于 Java 的工具,可根據(jù)用戶輸入計算 21 種拓?fù)涞碾妷汉碗娏鳎兄诩涌祀娫丛O(shè)計。另外,Power Stage Designer 包含波特圖繪圖工具和具有各種功能的實用工具箱,讓電源設(shè)計更簡單。這款工具可以非常快速地開始全新的電源設(shè)計,因為所有計算都是實時執(zhí)行的。·“Topology”窗口 – 根據(jù)輸入?yún)?shù)提供拓?fù)湫畔⒑驮ㄐ巍oop Calculator – 有助于確定不同拓?fù)涞难a(bǔ)償網(wǎng)絡(luò)·Load Step Calculator –

- 關(guān)鍵字: TI 開關(guān)模式電源 Power Stage Designer

Arasan宣布立即推出第二代MIPI D-PHY

- Arasan Chip Systems宣布立即推出其第二代MIPI D-PHY IP產(chǎn)品,支持MIPI D-PHY v1.1,速度高達(dá)1.5gbps,支持MIPI D-PHY v1.2,速度高達(dá)2.5gbps,用于GlobalFoundries 22nm SoC設(shè)計,重新設(shè)計了超低功耗和面積。這兩款產(chǎn)品的獨特之處在于MIPI D-PHY IP v1.1 IP針對可穿戴設(shè)備和物聯(lián)網(wǎng)顯示應(yīng)用的超低功率進(jìn)行了進(jìn)一步優(yōu)化,這些應(yīng)用的小型低分辨率屏幕需要最小的吞吐量,但功率至關(guān)重要。 D-PHY IP

- 關(guān)鍵字: Arasan MIPI D-PHY

開始使用 Power Stage Designer 的 13 個理由

- 十多年來,德州儀器 (TI) 的 Power Stage Designer? 工具一直是一款出色的設(shè)計工具,可協(xié)助電氣工程師計算不同電源拓?fù)涞碾娏骱碗妷骸N艺J(rèn)為,利用這款工具可以輕松開始全新的電源設(shè)計,因為它可以實時執(zhí)行各種計算,并為您提供直接反饋。 我們最新版本的 Power Stage Designer 在其現(xiàn)有功能集之上添加了一個新拓?fù)浜蛢蓚€新的設(shè)計功能,可幫助您進(jìn)一步縮短開發(fā)電源的設(shè)計時間。 新工具包含場效應(yīng)晶體管 (FET) 損耗計算器、并聯(lián)電容器的電流共享計算器、交流/直流

- 關(guān)鍵字: Power Stage Designer 德州儀器

chiplet phy designer介紹

您好,目前還沒有人創(chuàng)建詞條chiplet phy designer!

歡迎您創(chuàng)建該詞條,闡述對chiplet phy designer的理解,并與今后在此搜索chiplet phy designer的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對chiplet phy designer的理解,并與今后在此搜索chiplet phy designer的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司