模擬芯視界 | 優(yōu)化放大器電路中的輸入和輸出瞬態(tài)穩(wěn)定時間

在上期中,我們探討了HotRod? QFN 封裝技術(shù)與舊式封裝的對比,說明了它如何提升小型DC/DC電源轉(zhuǎn)換器的功率密度和整體性能。

本期,為大家?guī)淼氖?/span>《優(yōu)化放大器電路中的輸入和輸出瞬態(tài)穩(wěn)定時間》,將討論基于運算放大器電路中,輸入階躍瞬態(tài)與輸出負(fù)載瞬態(tài)響應(yīng)時間的差異問題,特別是針對一種常用于驅(qū)動容性負(fù)載的帶隔離電阻的雙反饋電路。

引言

運算放大器電路通常在執(zhí)行系統(tǒng)功能時需要響應(yīng)輸入和輸出瞬態(tài)。部分電路主要設(shè)計用于接受不同的輸入瞬態(tài),如傳感器信號調(diào)節(jié)電路;而其他電路則提供輸出瞬態(tài),例如模數(shù)轉(zhuǎn)換器 (ADC)輸入或基準(zhǔn)驅(qū)動器。在運算放大器電路設(shè)計中,同一電路的輸出(負(fù)載)階躍與輸入階躍的輸出穩(wěn)定響應(yīng)時間的差異經(jīng)常被忽視。

在大多數(shù)電路中,輸出負(fù)載直接連接到運算放大器的輸出端;響應(yīng)時間在很大程度上基于運算放大器對所需負(fù)載瞬態(tài)及后續(xù)恢復(fù)提供支持的能力。然而,該行為取決于電路拓?fù)洹T谶\算放大器輸出電壓 (Vopa) 不直接連接到負(fù)載的電路中,輸出穩(wěn)定響應(yīng)會與輸入響應(yīng)大不相同。在放大器必須驅(qū)動容性負(fù)載 (Cload) 的情況下,此類電路的一個常見示例是具有雙反饋 (Riso+DFB) 電路拓?fù)?/span>的隔離電阻器。在 Vopa 和 Cload 網(wǎng)絡(luò)之間使用隔離電阻器 (Riso) 并存在從反饋電容器 (Cf) 和反饋電阻器 (Rf) 返回反相輸入 (IN-) 的兩個反饋路徑,此電路也因此得名。

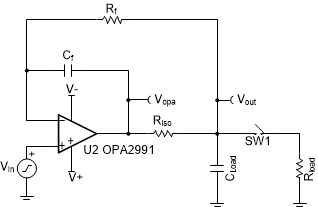

圖 1-1 顯示了一個用于驅(qū)動容性負(fù)載 (Cload) 的 Riso+DFB 電路示例。輸入端直接連接到電壓源,因此運算放大器必須對輸入端發(fā)生的變化做出反應(yīng)。在含有一個簡單的開關(guān) (SW1) 和電阻負(fù)載 (Rload) 的基本情況下,放大器電路必須對輸出端出現(xiàn)的負(fù)載瞬態(tài)做出響應(yīng)。

圖 1-1 具有雙反饋的 Riso 原理圖

圖 1-2 中的兩個仿真電路展示了輸入階躍和負(fù)載瞬態(tài)輸出響應(yīng)之間的差異。圖 1-2(a) 將輸入電壓階躍應(yīng)用于電路的輸入端,而 圖 1-2(b) 將負(fù)載電流階躍應(yīng)用于輸出端。在負(fù)載瞬態(tài)電路中,通過將流經(jīng) Riso (Iload x Riso) 的負(fù)載電流 (Iload) 形成的輸出壓降設(shè)置為與輸入階躍幅度相等,將兩個電路中 Vopa 的初始變化設(shè)置為 10mV,從而實現(xiàn)同級比較。10mV 的輸出階躍幅度可防止運算放大器出現(xiàn)大信號趨穩(wěn)行為,例如壓擺率限制。此外,輸出電流必須足夠小,以防止運算放大器進(jìn)入大信號短路電流限制范圍。

圖 1-2 輸入階躍 (a) 和負(fù)載瞬態(tài) (b) 仿真電路

圖 1-3 顯示了兩個仿真電路的結(jié)果。按照設(shè)計,針對輸入和輸出響應(yīng),Vopa 的初始變化均為 10mV。但是負(fù)載輸出電壓 (Vout) 穩(wěn)定所需的時間在兩個電路之間是不同的;輸入階躍電路的趨穩(wěn)速度比輸出負(fù)載瞬態(tài)階躍電路快得多。例如,若要穩(wěn)定到 0.05%(相當(dāng)于 10 位),輸入階躍電路需要 5.02μs,輸出負(fù)載瞬態(tài)電路需要 189.42μs。

表 1-1 列出了圖 1-2 中輸入階躍電路和負(fù)載瞬態(tài)階躍電路要實現(xiàn) 10 至 18 位分辨率采集系統(tǒng)所需的輸出穩(wěn)定時間之間的差異。由于不同的輸出阻抗和開環(huán)增益曲線會造成更加細(xì)微的影響,測試備選運算放大器將獲得不同的穩(wěn)定響應(yīng)。

表 1-1 不同穩(wěn)定精度水平的輸入和輸出瞬態(tài)穩(wěn)定時間

圖 1-3 輸入階躍 (a) 和輸出負(fù)載瞬態(tài) (b) 電路的

輸出穩(wěn)定響應(yīng)

圖 1-4 顯示了對輸入和輸出瞬態(tài)的輸出穩(wěn)定響應(yīng)起主導(dǎo)作用的元件,如紅色箭頭所示。對于輸入階躍瞬態(tài),Riso 和 Cload 電阻-電容 (RC) 時間常數(shù)決定了輸出穩(wěn)定時間。發(fā)生輸入階躍時,Vopa 立即響應(yīng)輸入電壓階躍。隨著運算放大器輸出電壓升高,Vout 會因 Riso 和 Cload 而出現(xiàn)延遲。

對于負(fù)載瞬態(tài),Rf 和 Cf RC 時間常數(shù)決定了輸出穩(wěn)定響應(yīng)。發(fā)生負(fù)載瞬態(tài)時,Vout 立即下降 10mV (Riso x Iload)。Vopa 響應(yīng) Vout 下降所需的時間取決于 Rf 和 Cf 產(chǎn)生的 RC 延時時間。

圖 1-4 主導(dǎo)輸入階躍 (a) 和輸出負(fù)載 (b) 瞬態(tài)響應(yīng)的

RC 時間常數(shù)

圖 1-5 將輸入階躍和負(fù)載瞬態(tài)輸出穩(wěn)定時間(底部響應(yīng))與前文所述的起主導(dǎo)作用的 RC 時間常數(shù)(頂部響應(yīng))進(jìn)行了比較。圖 1-5F(a) 將 Vout 的輸入階躍穩(wěn)定時間與具有 100Ω 電阻器和 10nF 電容器(Riso 和 Cload)的 RC 電路響應(yīng)進(jìn)行了比較。圖 1-5(b) 將輸出瞬態(tài)穩(wěn)定時間與具有 100kΩ 電阻器和 270pF 電容器(Rf 和 Cf)的 RC 電路響應(yīng)進(jìn)行了比較。RC 電路上升時間與輸入階躍和負(fù)載瞬態(tài)輸出穩(wěn)定響應(yīng)一致,從而證實了上述理論。

圖 1-5 輸入階躍 (a) 和輸出負(fù)載 (b) 瞬態(tài)穩(wěn)定時間

(RC 時間常數(shù)起主導(dǎo)作用)

下文將討論 Riso+DFB 電路的穩(wěn)定性標(biāo)準(zhǔn),并介紹如何優(yōu)化反饋比,以獲得更好的負(fù)載瞬態(tài)穩(wěn)定時間。首先,運算放大器作為單位增益緩沖器,必須穩(wěn)定驅(qū)動 Riso+Cload 組合。其次,由 Rf 和 Cf 形成的 1/Beta 極點必須至少小于來自 Riso 和 Cload 的零點頻率的一半。

·單位增益緩沖器驅(qū)動 Riso x Cload 的相位裕度:>45°

·反饋比:(Rf x Cf)/(Riso x Cload) > 2

雖然穩(wěn)定運行的反饋路徑的最小比率為 2,但穩(wěn)定電路沒有最大比率。只要滿足第一個標(biāo)準(zhǔn),反饋路徑比率可穩(wěn)定保持在 10、100 甚至 1,000,并具有類似的相位裕度結(jié)果。然而,如 圖 1-5 所示,輸出負(fù)載響應(yīng)基于由 Rf 和 Cf 元件形成的時間常數(shù)。因此,雖然穩(wěn)定,但較大的比率將導(dǎo)致負(fù)載響應(yīng)比輸入響應(yīng)慢得多。

圖 1-6 顯示了輸出穩(wěn)定響應(yīng)如何隨改變 (Rf x Cf)/(Riso x Cload) 的比率而化變。當(dāng)反饋比接近最小標(biāo)準(zhǔn) 2 時,輸入階躍和輸出負(fù)載瞬態(tài)的輸出響應(yīng)幾乎相等,但會增加一些過沖和振鈴。增加 (Rf x Cf )/(Riso x Cload) 的比率會產(chǎn)生更大的阻尼輸出,一旦比率大于 20,該輸出對輸入階躍響應(yīng)的影響最小。然而,該比率對 Rf x Cf時間常數(shù)起主導(dǎo)作用,因此較大的比率會繼續(xù)增加負(fù)載瞬態(tài)輸出響應(yīng)時間。

圖 1-6 輸入階躍(頂部)和輸出負(fù)載(底部)瞬態(tài)的

多個比率的輸出穩(wěn)定響應(yīng)

因此,為了在響應(yīng)輸出負(fù)載瞬態(tài)時實現(xiàn)卓越性能,應(yīng)在設(shè)計電路時采用接近 2 的 (Rf x Cf )/(Riso x Cload) 比率。由于運算放大器特性與電路元件和多樣性之間的相互作用將導(dǎo)致某些組合低于目標(biāo)比率,更保守的設(shè)計方法將此比率設(shè)置在 4 和 10 之間。反饋元件比率低于 2 將影響電路的穩(wěn)定性。

這種效應(yīng)發(fā)揮作用的一個實際例子是 ADC 基準(zhǔn)驅(qū)動電路,如圖 1-7 所示。

圖 1-7 ADC 基準(zhǔn)驅(qū)動電路

在 ADC 的轉(zhuǎn)換階段,逐次逼近過程中會將內(nèi)部電容器數(shù)模轉(zhuǎn)換器 (CDAC) 組切換到電路中。每次新的電容器切換到電路中時,外部驅(qū)動電路所需的電流突發(fā)將作為負(fù)載瞬態(tài)出現(xiàn)。因此,如果沒有正確配置電路反饋比,Riso+DFB 電路可能無法正確穩(wěn)定至負(fù)載響應(yīng)。

圖 1-8 顯示了電路仿真中的上述效應(yīng),其中使用 圖 1-7 中的運算放大器電路作為 ADS8860 的基準(zhǔn)緩沖器,ADS8860 是一個 16 位逐次逼近寄存器 ADC,在本示例中配置為以 100kSPS 的速率進(jìn)行采樣。將電路中的反饋路徑比值從大約 3.6 變化到 360 顯示了負(fù)載穩(wěn)定時間的差異。正如圖 1-5 中的結(jié)果所預(yù)期,具有較高比率的電路需要更長的時間使基準(zhǔn)緩沖器電路達(dá)到平衡,從而導(dǎo)致轉(zhuǎn)換之間的最低有效位穩(wěn)定誤差小于 1/2。

最低模擬比率 – 圖 1-8(a) 中的 3.6 – 需要大約四個樣本達(dá)到平衡,而圖 1-8(c) 中比率為 360,需要超過 400 個樣本(或大約 4ms)電路才能達(dá)到平衡,這很好地說明這一點。應(yīng)用通常采用間歇性的樣本突發(fā),對于具有圖 1-8(c) 所示結(jié)果的電路可能不會在樣本突發(fā)完成之前完全達(dá)到平衡。不穩(wěn)定的基準(zhǔn)會導(dǎo)致出現(xiàn)轉(zhuǎn)換錯誤和 AC 性能下降。如前所述,比率為 3.6 和 360 的電路的相位裕度和輸入響應(yīng)幾乎相同;如果您沒有正確設(shè)計電路并驗證輸出負(fù)載響應(yīng),則可能會出現(xiàn)意外的電路結(jié)果。

圖 1-8 不同反饋比率的 ADC 基準(zhǔn)驅(qū)動趨穩(wěn):

3.6 (a);36 (b);和 360 (c)。左圖和右圖分別顯示了

5ms 時間標(biāo)度和 300μs 時間標(biāo)度,結(jié)果相同。

結(jié)論

包括 ADC 輸入和 ADC 基準(zhǔn)電壓驅(qū)動器在內(nèi)的應(yīng)用需要使用運算放大器電路對輸出負(fù)載瞬態(tài)和輸入階躍瞬態(tài)進(jìn)行響應(yīng)。這些應(yīng)用中經(jīng)常使用的 Riso+DFB 電路拓?fù)湓谳敵龊洼斎腚A躍的輸出穩(wěn)定響應(yīng)時間上會存在很大差異,具體取決于所選的電路值和比率。如果用戶在設(shè)計這些電路時僅使用輸入階躍進(jìn)行電路分析,則輸出負(fù)載穩(wěn)定可能會出現(xiàn)意外結(jié)果,從而對應(yīng)用產(chǎn)生負(fù)面影響。因此,在設(shè)計電路時,必須同時響應(yīng)輸入階躍瞬態(tài)和輸出負(fù)載瞬態(tài)。驗證對兩種瞬態(tài)類型的穩(wěn)定響應(yīng)是否滿足電路穩(wěn)定要求,這不失為一個好方法。

評論