為什么越小的去耦電容越靠近電源管腳放置?

因為數字電路,所以有大量的數字電路輸出的“0”“1”翻轉導致,需要大量的去耦電容。

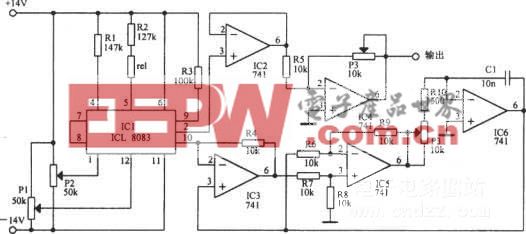

圖中開關Q的不同位置代表了輸出的“0”“1”兩種狀態。

假定由于電路狀態轉換,開關Q接通RL低電平,負載電容對地放電,隨著負載電容電壓下降,它積累的電荷流向地,在接地回路上形成一個大的電流浪涌。

隨著放電電流建立然后衰減,這一電流變化作用于接地引腳的電感LG,這樣在芯片外的電路板“地”與芯片內的地之間,會形成一定的電壓差,如圖中VG。同樣的對于電源端,每次信號翻轉,都會引入了電壓差。

當N多的翻轉出現的時候,我們需要運用去耦電容,去耦電容可以防止這種噪聲向外傳播,所以我們放一些電容靠近器件的電源管腳。

由于去耦電容一般對電容器的精度沒有很嚴格要求,選用時可根據設計值,選用相近容量或容量接近的電容器就可以。

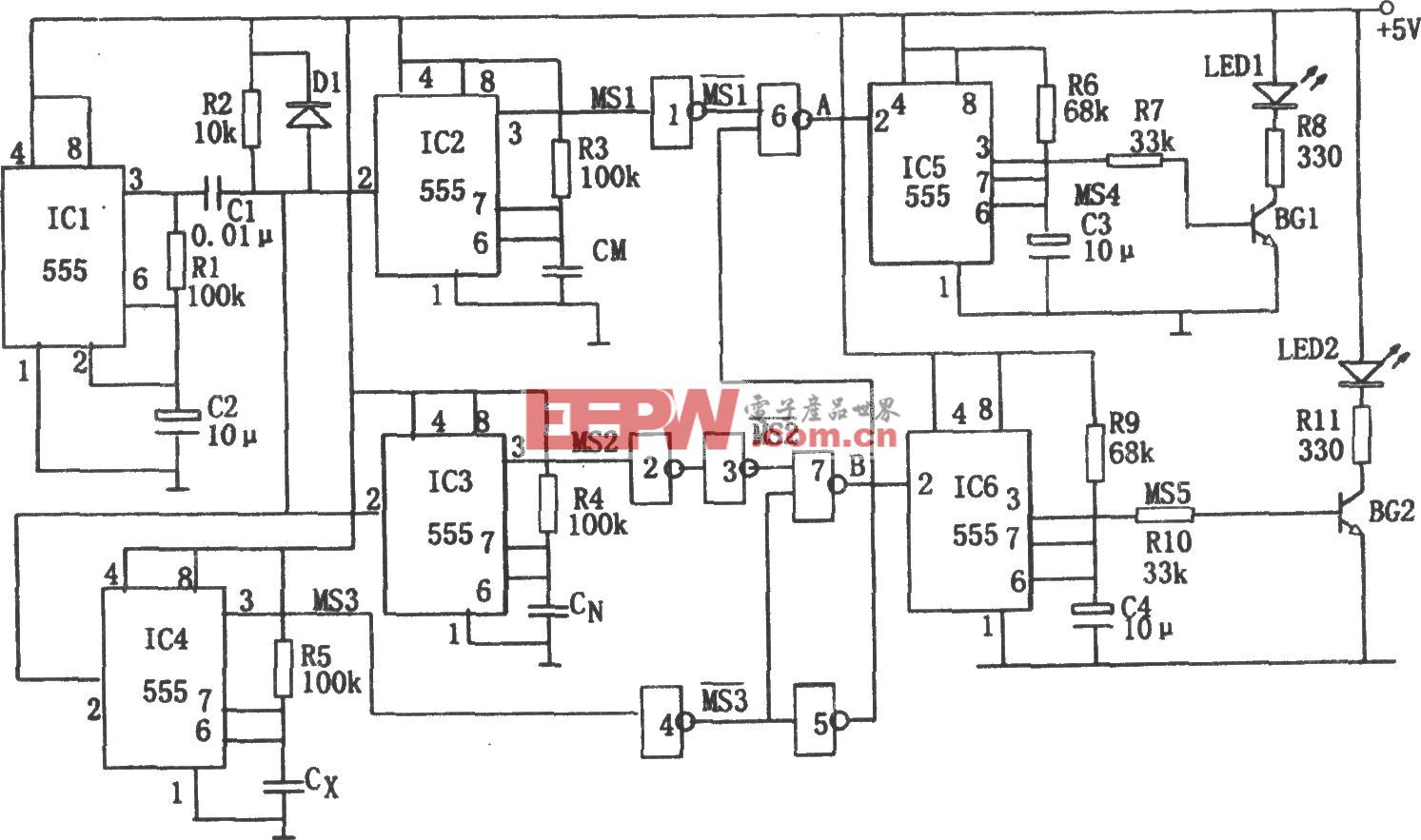

實際的電容存在寄生電感與等效串聯電阻。由于單個電容的ESR、ESL相近,他們的阻抗特性也是相近的,單個電容與多個特性相同的電容并聯阻抗特性圖

容值不同的電容

所以在這個場景中,我們需要一種:

1、1nF~10uF容量,精度要求不高;

2、由于用量比較大(電源管腳比較多),成本比較低、相同容量情況下體積比較小的電容;

3、ESR、ESL比較小的電容。(需要去耦的信號頻率比較高,并保證去耦效果)多層片陶瓷電容(MLCC)就顯得非常合適。

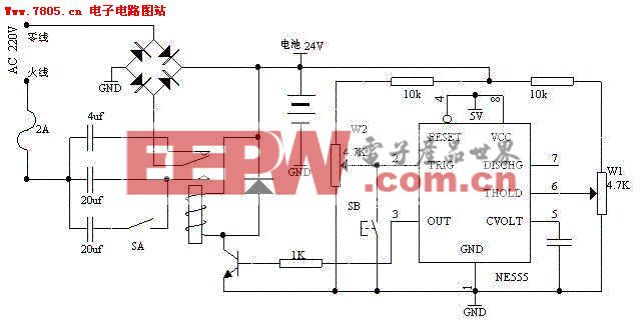

如下圖所示:容值越小的去耦電容越靠近電源管腳放置!

容值小的電容,有最高的諧振頻率,去耦半徑小,因此放芯片近一點,容值大的電容,其諧振頻率低,去耦半徑大,可以稍遠一點,電容的等級大致遵循10倍關系,以此在有效頻段出現低阻抗通道。

電源系統的去耦設計的一個原則,就是在需要考慮的頻率范圍內,使整個電源分配系統的阻抗最低。

由于芯片特別是CPU、FPGA、DSP等,多IO、大功率芯片作為電路的核心,這些芯片的電源管腳也比較多,所以去耦電容的用量就比較大。

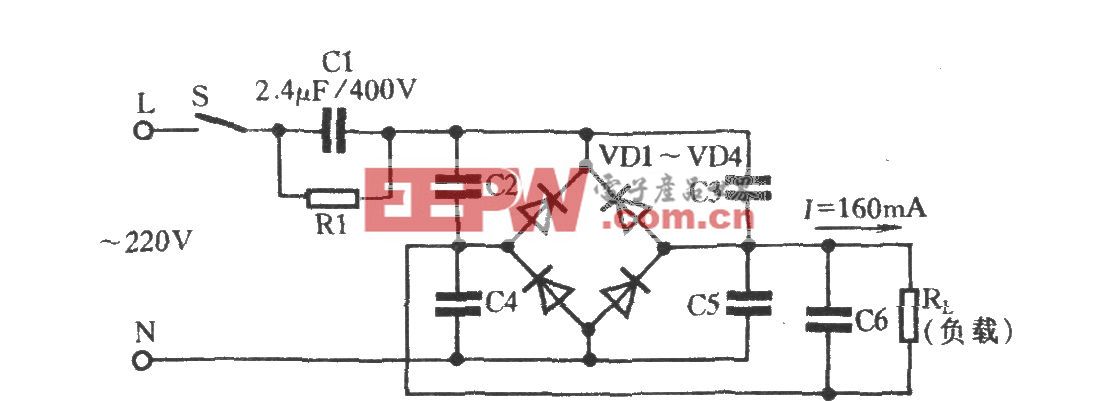

一般我們芯片由于速率越來越高,所以接口電平也就越來越低,導致我們的電路板上會有多種電壓值的電源,早期數字電路電源以5V、3.3V為主,現在數字電路電源越來越豐富:2.5V、1.8V、1.5V、1.1V、1.0V、0.9V,可調可控電源等等。所以這些開關電源的輸入電容和輸出電容也需要大量使用。

在 PCB 布局設計中,去耦電容(decoupling capacitors)的放置要求非常講究,尤其是容值較小的去耦電容需要靠近用電器件(如芯片、IC等)。這是基于以下幾個重要的原因:

1. 去耦電容的作用和頻率特性:

去耦電容的主要作用是濾除電源電壓中的高頻噪聲或脈動信號,提供平穩的電壓給敏感的用電器件。電容的作用與頻率密切相關:

容值越小的電容,頻率響應越高:容值小的電容在高頻下表現更好。它能夠快速響應高頻噪聲,因為它具有較低的阻抗(Z = 1/(2πfC)),能在高頻信號上起到更好的去耦作用。

由于高頻信號的波長很短,因此小電容需要在盡可能短的距離內提供去耦作用,否則信號會在電路中傳播較遠,導致去耦電容的效果降低。

2. 電流路徑和寄生效應:

小電容的 ESR 和 ESL 影響較大:小容值電容的等效串聯電阻(ESR)和等效串聯電感(ESL)相對較大,特別是在高頻時,這些寄生效應對去耦效果有較大影響。如果電容離用電器件較遠,信號通過PCB的寄生電阻和電感時,電容的去耦效果會受到衰減,尤其是在高頻區域。

信號的傳輸延遲和電流路徑:電流需要通過PCB的導線、接地平面等,才能到達電容。如果電容離用電器件太遠,信號傳輸路徑就會增加,導致電流路徑中的噪聲更加嚴重,電容就難以有效地濾除噪聲。更小的電容尤其需要短的路徑,以便快速響應高頻噪聲。

3. 寄生電感和電流傳遞速度:

小電容器由于容值小,其帶寬較寬,因此在高頻下需要更低的電感來保證有效去耦。如果電容太遠,PCB導線的電感會抵消電容器的去耦效果,導致去耦作用大大減弱。

電流在電路板上通過導線的傳播速度有限,因此容值較小的電容需要直接、快速地與用電器件連接,以減少信號衰減和延遲。

4. 短路徑能減小噪聲:

在高速電路中,信號的快速變化容易產生電磁干擾(EMI)或噪聲。為了減少這種噪聲,去耦電容需要盡可能地靠近用電器件,提供低阻抗的電流路徑,確保電源的電壓穩定,避免產生高頻噪聲。

容值小的電容可以更有效地應對這些快速的電壓波動,離用電器件更近有助于更快響應和消除干擾。

總結:

容值小的去耦電容需要靠近用電器件的原因,歸結于電容器的工作頻率特性、寄生效應、電流路徑和噪聲傳輸等因素。在高頻應用中,電容與用電器件之間的距離越近,去耦效果越好。容值小的電容器需要減少電流路徑中的寄生電感和電阻,才能高效地去除電源噪聲,保證系統的穩定運行。

評論