拯救英特爾Foundry一切都還剛剛開始

如果單從股價和財報上看,英特爾似乎已經走過了最艱難的日子,股價飆升80%,從巨額虧損到實現(xiàn)不小的季度盈利,以及自己18A工藝開始量產,諸多利好消息都在預示著這家昔日半導體霸主的2025 多么令人興奮,但真正的問題是,英特爾最尷尬的晶圓制造部門怎么樣了?

說起晶圓制造,雖然整個產業(yè)的產能利用率并不如2021年那么緊缺,但伴隨著AI 和汽車電子催生的半導體需求暴漲,幾乎沒有晶圓廠都接近滿負荷運轉(也許除了英特爾)。不提利潤率超4 成的臺積電,以及產能利用率持續(xù)超100% 的中國大陸兩大晶圓廠,英特爾沒吃下的Tower盈利能力大幅攀升,英特爾正在談合作成熟工藝的中國臺灣UMC業(yè)績長紅,甚至被中東財團散養(yǎng)的格羅方德都已經開始通過收購擴張業(yè)務范圍了。德州儀器今年宣布產能擴張進軍成熟工藝代工,三星美國工廠迎來特斯拉百億訂單,存儲器價格暴漲引發(fā)存儲廠商利潤率飆升。

面對如此“芯芯”向榮的2025 年,英特爾的制造部門卻在第三季度交出了一份下滑的成績單,這對于致力于將制造業(yè)務看作復蘇英特爾基石的所有人,都是一個尷尬而不失禮貌的答卷。

英特爾2025第三季度財報

1 18A,是英特爾的生命線?

2025年宣布量產的18A,是否會成為英特爾的生命線,這是一個值得思考的問題。從技術層面,18A 的發(fā)布證明了英特爾擁有跟臺積電和三星同等工藝水平的能力,但以產品力來說,也許僅僅是能力而已。

18A是基辛格整肅英特爾業(yè)務的終點(不管是計劃中還是意外中斷的),早在2021 年英特爾前首席執(zhí)行官帕特· 基辛格回歸英特爾之時就提出了全球IDM 2.0(集成設備制造商2.0)戰(zhàn)略,該戰(zhàn)略基于三個關鍵領域。

● 通過明確的計劃“四年五節(jié)點”恢復芯片生產的領先地位,計劃在四年內快速開發(fā)五項新工藝技術(Intel 7、4、3、20A、18A),以重新奪回對競爭對手的技術優(yōu)勢。

● 擴大與第三方工廠的合作:吸引競爭對手——主要是臺積電——生產Chiplet架構的單個組件(圖形單元、I/O芯片組等)的能力。

● 成立英特爾代工服務(IFS)——向第三方客戶開放自有生產設施,使英特爾成為一家全面的合同制造商,與臺積電和三星競爭。

很明顯,這是一個能從根本上讓英特爾再次輝煌的計劃,但這個計劃也是一個需要大量投入的計劃,在執(zhí)行計劃中英特爾迅速惡化的財務報表直接導致了第二次CEO提前黯然離開。

18A同樣是陳立武重建英特爾的起點,陳立武并沒有放棄將英特爾制造作為公司未來核心業(yè)務的戰(zhàn)略方向。最初的“四年五節(jié)點”的計劃,盡管存在一定保留,但實際上已經實現(xiàn)或接近這一階段。當陳立武舉起18A工藝晶圓片笑著出現(xiàn)在鏡頭前,卻沒有任何客戶為英特爾的代工業(yè)務埋單,這個問題還要考慮到美國本土制造芯片呼聲下,英特爾是唯一一家美國擁有3nm 以下工藝晶圓廠。甚至英特爾自己的產品線為了增加產品性能競爭力,選擇在臺積電的工廠代工。

雖然已經收獲了軟銀的投資以及英偉達的聯(lián)合開發(fā)入股,讓英特爾的股價來到了上任之初承諾的價位,但是在可能是英特爾公司最了解半導體生態(tài)系統(tǒng)的陳立武心中,18A的成敗幾乎決定了能不能讓自己2500 萬美元購買的英特爾股份成功保值。

據傳,當年主導臺積電在工藝上實現(xiàn)對英特爾趕超的關鍵“夜鷹”計劃的負責人羅唯仁已經“鐵心”要重返奮斗了十多年的英特爾,助力英特爾制造業(yè)務重奪領先位置。

2 這一次換英特爾奮起直追了

那么用四年時間跨越5個節(jié)點到達的18A 究竟如何呢?回顧的開端,我們還要從令人琢磨不透的Intel 7 開始。10nm 時代的英特爾還是半導體工藝的領先者,但隨后英特爾似乎迷失了方向,有人說是銅鎢材質的糾結讓英特爾被臺積電后來居上,曾經一直跟隨英特爾開拓出來的正確工藝研發(fā)路徑的臺積電先于英特爾找到了銅合金的處理方法。

向Intel 7工藝技術的過渡可能是技術上最容易實現(xiàn)的,當然從時間過程上卻是最漫長的。事實上,Intel 7是另一項改進的10 納米芯片制造技術。英特爾可能最專注于改進該節(jié)點,基于它發(fā)布了多代CPU。英特爾7 不僅僅是簡單工藝節(jié)點重塑,與之前的10 納米SuperFin 相比,得益于額外的優(yōu)化,Intel 7(增強型SuperFin)每瓦能耗性能提升10–15%。2021 年底,Alder Lake 芯片使用的是Intel 7,后來Raptor Lake和Raptor Lake Refresh(Intel Core 12/13/14世代)也加入了。這也包括Sapphire Rapids 系列服務器處理器。

下一步技術是Intel 4工藝技術。這是一個相當重要的進步,因為英特爾為在短期內完成其實現(xiàn)方式,從深紫外光刻(DUV 光刻)轉向極紫外(EUV)。這種波長更短(13.5 納米對193 納米)的新技術使晶體管尺寸縮小并顯著提高了密度。使用DUV 技術生產需要多次曝光,這使工藝復雜化,增加掩膜數量,并增加缺陷風險,這在7 納米以下的工藝尤為關鍵。極紫外光允許大多數層進行單次曝光,這也提高了晶體制造速度。極紫外也有缺點,比如光源是基于錫的激光等離子體,效率較低且設備功耗更高。此外,采用多層涂層的復雜鏡面系統(tǒng)代替折射光學,這種系統(tǒng)對污染非常敏感,甚至納米顆粒也可能在晶體中造成缺陷。當然,EUV的實現(xiàn)需要重新設計芯片設計、光罩和制造工藝,因此對于從DUV轉型的企業(yè)來說,這并非易事。極紫外光刻設備成本顯著高昂,因此只有極少數公司能夠負擔使用極紫外大規(guī)模生產芯片,英特爾邁過這一步并不讓人意外,但基辛格引領的這一步卻意義非凡,因為這是英特爾保留追趕臺積電和三星希望的最關鍵一步,也是英特爾加速工藝開發(fā)節(jié)點的真正意義第一步。

英特爾采用Intel4工藝技術制造Meteor Lake(Core Ultra 1xx)移動處理器系列,主要用于帶計算核心的主芯片組,而選擇臺積電N5用于集成顯卡晶體,臺積電N6用于芯片晶體芯片和I/O芯片,大概是英特爾首款采用不同廠商晶體組合的量產芯片。這生動地體現(xiàn)了公司在生產范式上更開放和變革的體現(xiàn)。也許這是強制措施,但與第三方廠商的合作符合英特爾新的變革理念。

緊隨其后的Intel 3工藝比Intel 4更直接、更快速地實現(xiàn)。由于英特爾4 是首個廣泛實現(xiàn)EUV 光刻技術的節(jié)點,英特爾3利用這一經驗顯著優(yōu)化制造的各個方面。英特爾聲稱,升級后的Intel 3 節(jié)點在相同功耗下比英特爾4提升了多達18%的性能(或顯著降低了功耗)。此外,得益于引入新的高密度標準單元庫,Intel 3 相比Intel 4實現(xiàn)了約10%的晶體管密度提升。

如果比較Intel 3和臺積電N3工藝技術的性能,這兩者名義上屬于“3 納米”級別,不過臺積電的3 nm工藝晶體管密度更高。根據公開的數據,臺積電N3的升級版可達到每平方毫米1.9億至2.1億個晶體管,而Intel 3的密度為每平方毫米1.5億個晶體管。因此,從該指標來看,Intel 3更像是臺積電N4的競爭對手(1.45億至1.7億晶體管/ 平方毫米,即“4納米級”)。

當然晶體管密度只是半導體工藝關鍵參數之一,據介紹Intel3 更適合高性能芯片和最大化工作頻率,而TSMS N3 在為移動設備制造芯片方面具有優(yōu)勢,重點是提升能效。象征意義上,Intel 3 成為該公司最后一個采用FinFET 晶體管架構的節(jié)點,隨后英特爾實現(xiàn)向GAA(全能門)結構的根本轉變——柵極被門完全包圍。

Intel 20A 工藝比較特別,從名義上它超越了同期的臺積電3nm 工藝,它同時實現(xiàn)了兩項基礎創(chuàng)新——RibbonFET 和PowerVia。第一種實現(xiàn)了新的晶體管結構,采用納米色帶通道,完全被柵極(GAA)包圍; 而PowerVia 則將電源軌移至晶體底部,晶體管層下方,從而降低損耗并提高元件密度。英特爾最初計劃于2024年上半年開始Intel 20A 的試點生產,據傳在該技術開發(fā)過程中,在改進下一代節(jié)點Intel 18A 方面取得了顯著進展,該節(jié)點展現(xiàn)出更好的穩(wěn)定性和可用芯片的良率。鑒于此,英特爾決定將資源集中于加速向Intel 18A的過渡,限制了Intel 20A 的實現(xiàn)規(guī)模。根據分析估計,這一步驟使公司節(jié)省了約5 億美元,并縮短了達到更先進生產標準的時間。因此,最終Intel 20A 成為測試晶體管整體結構和電源技術深度變革的實驗節(jié)點。

基辛格的“4 年5 節(jié)點”計劃的終極目標是首批Intel 18A 芯片將在2024 年下半年推出,當然最終的量產時間晚了6 個月左右,從速度角度來說已經很讓人驚嘆了。英特爾的18A 工藝技術是“埃時代”中首個真正成熟的下一代節(jié)點,結合了兩項基礎創(chuàng)新——RibbonFET 晶體管架構和PowerVia 反向電源技術,這是該組合將首次在業(yè)內使用。英特爾18A 屬于“1.8 納米級”,有望與臺積電N2(2 納米)競爭。不過從量產時間點來看,英特爾的18A 似乎取得領先,但從實際產品上,似乎誰更能大批量(10 萬片晶圓級別)交付給客戶還不好說。

英特爾可以在單個芯片內調整納米片的寬度,以優(yōu)化速度或功耗。這允許對單個晶體管特性進行更細致的調優(yōu)——例如“性能”和“效率”CPU 核心。由于柵極控制更佳,帶狀FET 需要更低的開關電壓,從而減少散熱并提升功率效率。向GAA 晶體管結構的轉變對于高密度技術節(jié)點(小于5 納米)尤為基礎。上一代FinFET 在較大規(guī)模上表現(xiàn)相當高效,但隨著晶體管尺寸減小,通道變得過短,柵極無法完全控制導電性——通道的靜電控制會逐漸衰弱。即使晶體管應關閉,電流仍會“泄漏”通過通道的下半部,而柵極無法控制。短通道效應會產生,降低性能、可靠性,并顯著增加靜止功耗。帶狀場效應晶體管通過提供全信道控制、垂直堆疊多納米絲帶的能力以及減少晶體管間的最小間隙,提高了晶體管密度。這使得比FinFET 更多的有源元件可以在同一芯片面積上放置,而不失去可控性或增加泄漏電流。

使用帶有GAA 結構的晶體管的想法并不新穎。三星在其3 納米的三星SF3E 工藝中率先采用了類似架構,該工藝于2022 年年中推出,三星將其解釋為MBCFET(多橋通道FET)。其基本原理與帶狀FET 相同。納米帶的具體尺寸、厚度以及用于制造柵欄和帶狀物間填充物的材料可能有所不同。臺積電公司計劃為臺積電N2 工藝技術開發(fā)自有的GAA 變體。預計該節(jié)點的量產時間為“2025 年底至2026 年初”。因此,實際作也在逐步推進中。臺積電的GAA 技術沒有像英特爾(RibbonFET)或三星(MBCFET)那樣的獨特商業(yè)名稱。臺積電將其GAA 架構簡稱為“納米片”,或使用GAAFET(全能門FET)的通用名稱。

但真正讓英特爾領先競爭對手的是同時使用GAA(RibbonFET)晶體管架構和BSPDN(后側電源傳輸網絡)電源技術,英特爾將其解讀為PowerVia。PowerVia徹底改變了功耗管理的做法。傳統(tǒng)上,電力線是放置在晶體管層上方,現(xiàn)在它們鋪設在晶體管層下方,穿過晶體背面。這種供電方式可以釋放上層用于信號連接,減少電損耗,減少信號延遲并提高能源效率。

將電源線移到芯片后方可以降低電阻和IR 下降,這對高時鐘芯片至關重要。這項技術使英特爾有可能實現(xiàn)更高時鐘頻率或更高效的高性能核心,因為它釋放了前端信號線空間,從而改善了布線。英特爾的主要競爭對手也在計劃自己實現(xiàn)BSPDN。臺積電將立即在其升級后的N2P 節(jié)點上測試超級動力軌道技術。預計將以下一個工藝技術臺積電A16 開始量產,該技術暫定于2026 年下半年開始投產。三星還計劃為2 納米SF2Z 和SF1.4(1.4 納米級)工藝技術分開信號線路和電源通道,這些工藝僅于2027 年推出。

3 RibbonFET + PowerVia組合

英特爾對Intel 18A 關鍵創(chuàng)新協(xié)同效應的期待是什么?研發(fā)人員保證,新工藝將在相同性能下實現(xiàn)超過25% 的功耗降低。或者,換個角度,我們可以考慮芯片在相同功耗水平下以更高頻率運行的可能性。與英特爾3 工藝技術的性能相比,英特爾18A 每瓦能耗的性能提升可超過15%。同時,采用Intel 18A 工藝技術的晶體管間距比Intel 3 高出多達30%。這允許在相同尺寸的芯片上放置更多功能模塊,或減小晶體尺寸,直接影響生產成本。

至于整體制造成本,使用PowerVia 相比之前的工藝技術略有提升,但由于成本結構的變化,差異仍屬適度。PowerVia 技術可以降低晶體前端(前端)的復雜性和成本,減少對面罩的需求和技術步驟的數量。這在一定程度上彌補了技術本身帶來的額外成本。英特爾表示,PowerVia 的實施在經濟上是可行的解決方案。

4 英特爾18A的生產能力

向新的生產技術標準的過渡是一個非常艱難的過程,當我們談論的不是研究和實驗開發(fā),而是規(guī)模化和大規(guī)模生產時,過程變得更加復雜。英特爾18A 的實際開發(fā)階段在俄勒岡州的現(xiàn)代研發(fā)基地英特爾Fab D1X進行,測試了未來節(jié)點的關鍵技術和原型。新的制造晶圓廠位于亞利桑那州錢德勒附近的Ocotillo 園區(qū)。Fab52 最近獲得了“全面運行”狀態(tài),確認了生產周期的建立和批量生產的準備。有趣的是,Ocotillo 園區(qū)距離鳳凰城市僅30 至40 公里,而潛在競爭對手臺積電已在郊區(qū)擴展了其工業(yè)基礎。其Fab 21 Phase 1 已在此運行,該廠采用4 納米工藝技術(臺積電N4)制造芯片。此外,臺積電計劃組建多家工廠集群,采用臺積電N2 和A16 工藝生產芯片。因此,亞利桑那州正迅速成為美國先進芯片生產的主要中心之一。工廠的靠近帶來了對高技能工程師和技術人員的競爭,同時也帶來了對當地資源——主要是水和電力——的便利。同時,強大的本地基礎設施以及設備和材料供應商(ASML、應用材料、藍研研究等)的集中對兩家公司都有利。

回到Fab 52,我們注意到英特爾18A 采用了低NA極紫外光刻設備,其曝光范圍為0.33。這些掃描儀——尤其是ASML NXE:3600D 和NXE:3800E 型號——是同代現(xiàn)代系統(tǒng),允許你形成關鍵特征尺寸。低NAEUV 技術用于最小層的帶狀FET 晶體管和PowerVia 金屬化,而對于不那么關鍵的層,英特爾繼續(xù)使用先進的DUV ArF 浸沒系統(tǒng)。

盡管高NA 極紫外線(0.55 光圈) 已經在開發(fā)中,英特爾計劃在18A 節(jié)點完全開發(fā)完成后才轉向該技術——很可能用于英特爾14A 及以下。至于英特爾18A,低NA EUV 結合改進的校準算法、多重曝光和精確的相位校正,使得在不犧牲性能的前提下實現(xiàn)了所需分辨率。

回顧ASML(EXE:5000 系列)最頂級的高NA 極紫外光刻安裝費用約為3.8 億美元,安裝和調試過程極其復雜且漫長。英特爾成為該光刻機的首個客戶,該設備已在研究機構Fab D1X 中使用了一段時間。根據初步數據,英特爾18A 也將使用高孔徑掃描儀進行實驗,但此類設備將用于使用英特爾14A 工藝技術進行批量生產。

因此,低NA EUV 依然是英特爾向下一代架構——RibbonFET + PowerVia 轉型的關鍵工具,在技術復雜性、生產線質量和制造成本效益之間取得平衡。

Fab 52 高度自動化。300 毫米硅片儲存在特殊艙體(FOUP,前開通用艙)中,這些艙體通過架空輸送系統(tǒng)在不同設備間移動。整個“烘焙”晶體過程涉及數百個技術作和過渡,因此組件物流在這里至關重要。注意房間照明的特征黃色。這在光刻領域被使用,因為黃色光的波長不會激活硅晶圓上涂層的感光聚合物(光刻膠)。

實現(xiàn)帶狀FET 和PowerVia 相比傳統(tǒng)前饋FinFET技術,生產需要額外的技術步驟。帶狀FET 需要用“帶狀”替換經典的FinFET——即用柵極包裹的細通道。為了形成多層納米帶,需要通過生長或沉積多層硅的結構。還有一個高精度干蝕階段,用于隔離單個絲帶而不損壞相鄰色帶。在全套沉積時,金屬門在帶狀結構的四周沉積,材料穿透狹窄通道并控制空腔的缺失。

PowerVia 的實現(xiàn)同樣增加了技術復雜度。在這種情況下,基材厚度會減小,并對表面均勻度進行特殊控制。為了直接將功率傳遞到晶體管單元,使用了微觀的納米TSV(硅過孔)通道——這些極其細的導體作為微觀“橋”,穿過一層薄硅,將背面的電源線與晶體管層連接起來。這些納米 TSV 直接位于晶體管下方,以提供最短的功率路徑。從技術角度看,創(chuàng)建此類通道的過程類似于“大型”水槽——等離子體蝕刻以制造空腔,涂覆壁面并用導體(銅)填充孔洞,但由于直徑極小,常規(guī)過程變成了現(xiàn)代物理和工程學的極具挑戰(zhàn)性的生產挑戰(zhàn)。

5 Intel 18A工藝的良率

關于英特爾18A工藝技術的可用芯片的良率問題仍存在爭議。英特爾未正式披露相關指標,聲稱當前產量符合當前生產階段的計劃內部指導方針,并且對首批產品的發(fā)布時間表充滿信心。與此同時,英特爾首席財務官大衛(wèi)· 津斯納承認,收益率尚未達到預期盈利水平。根據非官方估計,這一數字可能在30% 至50% 之間波動,但這些數字也只是大致估計。英特爾預計芯片良率將繼續(xù)與標準工藝改進曲線同步增長。研發(fā)團隊設定了2025 年底的具體目標,鑒于當前缺陷率下降的趨勢,期望的結果將實現(xiàn)。

到2026 年底,收益率應達到保證預期成本和正常利潤率的水平。到2027 年,這些指標應達到成熟技術流程的行業(yè)產率標準(超過70%)。因此,盡管英特爾18A 目前的良率可能低于穩(wěn)定且成熟的技術工藝,但足以推出首批商業(yè)產品并展示技術能力。

6 英特爾14A與向高NA EUV的過渡

雖然技術人員專注于提升適合英特爾18A芯片的良率,研發(fā)部門已積極研發(fā)下一代芯片——英特爾14A(1.4 納米級)。該節(jié)點實現(xiàn)了更薄的技術規(guī)范,升級了帶狀FET 2 晶體管結構,PowerDirect 技術——PowerVia 的進一步發(fā)展,新的單元庫以及更寬的閾值電壓范圍。一套不錯的技術優(yōu)化,既對自身生產也有需求,滿足高要求客戶的需求。

英特爾有信心能夠提供具有極具競爭力的PPA(功率、性能、面積)解決方案,即性能、功耗和面積的比值。英特爾14A 的試點生產已計劃于2027 年進行。技術標準和架構優(yōu)化的進一步提升應當帶來顯著的實際成果。預計密度較Intel 18A 提升約30%。每瓦性能應提升15-20%,整體功耗應減少25-35%。

對于英特爾14A 最關鍵層的生產,高NA 極紫外光刻技術是不可或缺的。我們已經提到了安裝此類設備的成本和復雜性。因此,向下一技術階段的過渡將需要額外的財務成本。英特爾已經警告稱,采用英特爾14A 技術生產芯片的成本將高于英特爾18A 節(jié)點的工藝。預測哪個組成部分會增加生產成本并不難。然而,即便如此,最先進的水晶仍會有客戶。制造商能否根據新標準及時掌握并實現(xiàn)大規(guī)模生產的問題在這里依然具有重要意義。

甚至在英特爾14A 大規(guī)模部署之前,制造商就會推出一款針對更高功頻比優(yōu)化的Intel 18A-P 變體。據稱,與基礎版Intel 18A相比,每瓦性能提升高達~8%,同時保持設計規(guī)則的兼容性。隨后還將推出Intel 18A-PT的變體,重點應用于復雜異構集成(芯片組垂直堆疊)的芯片,需要使用透硅通孔(TSV)。

7 英特爾Foundry的現(xiàn)狀與未來

英特爾的制造部門已經不再只是為自己制造芯片的私有團隊,從基辛格到陳立武,他們都堅信英特爾的制造部門應該可以用來為公司創(chuàng)造利潤。雖然,目前還很少有英特爾這樣的IDM 轉型為代工廠的成功案例,但既然德州儀器也追隨同樣的路線,那么證明這條路并不是完全沒有機會,特別是考慮到越來越多美國企業(yè)開始自己設計芯片,并且要求在美國本土生產。

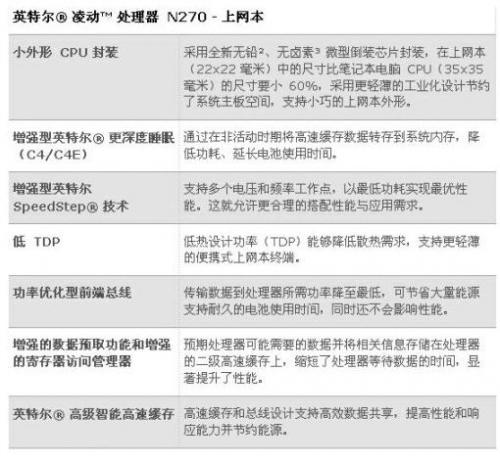

為了評估半導體行業(yè)的前景和當前規(guī)模,我們呈現(xiàn)一張按技術標準和預計收入分布的示意圖。據Counterpoint Research統(tǒng)計,僅在過去四年,合同制造領域參與者的全球收入增長了60%,從1050億美元增長到1650億美元。同時,超過50%的技術工藝仍由5納米以上的工藝帶來。此外,這里的更大比例是28+nm。這就引出了“過時”技術節(jié)點的相關性問題。

來源:Counterpoint Research

根據上半年業(yè)績,合同制造市場的分布如下:臺積電依然是無可爭議的領頭羊,其份額已超過 70%,并持續(xù)逐步增加 ;8% 屬于三星代工,5% 分別屬于 SMIC 和 UMC。GlobalFoundries 以 4% 的增長率進入前五名。其他所有成員合計占 8%。正如我們所見,目前英特爾未被列入相應評級,屬于未具名的“其他”類別。

不過英特爾代工業(yè)務最尷尬的問題是,英特爾似乎更希望將Intel 14A 作為代工服務的主節(jié)點。雖然我們前面談論了很多Intel 18A 的技術領先性以及其工藝節(jié)點看起來同臺積電10 月剛量產的N2 工藝應該屬于同一代,但是目前極少有重要的客戶選擇英特爾代工服務,而即使三星的泰勒工廠至少還有8 個月才能竣工,都已經拿到了百億級別特斯拉訂單。

目前所有Intel 14A 的客戶消息都是感興趣,更多的是臺積電或三星兩家企業(yè)美國工廠的備選項,而這其中絕大部分客戶恰恰又是英特爾自己產品的潛在競爭者,不知道這種IDM+Foundry 模式是否影響力英特爾拿到客戶訂單,但有一點需要明確考慮,英特爾現(xiàn)在比較自信的18A 絕大部分研發(fā)工作是在基辛格任期實現(xiàn)的,而陳立武上臺后壓縮成本的策略對14A 的開發(fā)有多少影響是個大問號。

“4 年5 個節(jié)點”計劃交出的成績單應該說是差強人意的,但交出的經濟賬卻很尷尬,甚至可能恰恰是制造業(yè)務的支出拖累了過去幾年英特爾公司的整體財務情況,尤其是英特爾在業(yè)績不斷攀升的前提下利潤在持續(xù)萎縮。

不得不承認技術債務是真實存在的,如果你短期內因為技術跟不上進度而省錢,最終你總是在不得不追趕時付利息。或者,你會倒閉。英特爾正是如此,它在短時間內因愚蠢、傲慢和誠實的錯誤而幾乎變得無關緊要。

英特爾制造業(yè)務目前處境非常棘手,一邊是工藝提升需要大量資本支出,一邊是自己的處理器產品不斷委托臺積電代工割舍利潤,究竟內部核算中制造業(yè)務部門是分攤了其他部門的開銷,還是讓其他部門攤銷自己的額外支出,這點只有英特爾的財務人員知曉。難怪當被追問18A 的產能時,首席財務官津納發(fā)言遠遠多于CEO 陳立武,津納說了這樣一句話:

“產量足以應對供應問題,但還不足以達到我們需要的水平,無法實現(xiàn)相應的利潤率。到明年年底,我們很可能也會進入那個領域。而且,在那之后的一年,我認為他們的產量會達到行業(yè)可接受的水平。”

“我得告訴你,14A 我們開局非常好。如果你從14A 研發(fā)周期的角度來看,相對于同期的18A,我們在績效和收益率方面都更好。所以我們在14A 的開端更為順利。我們必須繼續(xù)推進這些進步。”

有趣的是,英特爾表示其服務器CPU 業(yè)務目前供應受限,部分原因是其現(xiàn)有Xeon CPU 所用Intel 3 和Intel 4工藝的容量有限,以及基底材料短缺,這影響了所有芯片制造商。不過至強系列曾經是英特爾最引以為豪的產品線,但現(xiàn)在,他們甚至都無法被自家次級工藝所覆蓋……

以下是津斯納的說法,我們之所以詳細引用他,是因為這很有道理:

“我認為有兩種動態(tài),其中之一是舊工藝的高成本與新工藝更優(yōu)成本結構的對立。這顯然意義重大。我的意思是,F(xiàn)oundry 已經進入了負毛利率的領域。如果你把它提升到積極的水平,那就是有意義的進步。”

“但我們毛利率的另一個方面,僅僅取決于產品質量。在產品性能和競爭力方面,我們對客戶的表現(xiàn)還算不錯,只有少數例外。但從成本角度來看,我們還沒達到應有的水平。因此我們必須在這方面做出改進。我們已經把這列入了路線圖。團隊也認識到這一點,但這是多年過程才能實現(xiàn)的。”

“在數據中心方面更明顯。我們不僅沒有合適的成本結構,也缺乏足夠的競爭力,無法真正從客戶那里獲得合適的利潤率。所以我們在那里有工作要做。這正是立武和團隊所追求、高度專注的,就是以合適的成本結構推出優(yōu)質產品,從而提升毛利率。對我來說,這才是這一切的關鍵。”

“鑄造廠方面的改進遲早會到來的,我想。我們會不斷提高到Intel 4、3,然后是18A,最終達到14A。這些公司的成本結構其實相當相似。這也取決于這些前沿節(jié)點所提供的價值將顯著增加,這將實質性地推動毛利率的提升。”

“我還想說的是,由于我們快速推進了大量新工藝,啟動成本大幅增加。進入14A 時,步頻會更正常。這樣你就不會看到那么多啟動成本疊加在一起,這會影響毛利率。這可是數十億美元。所以我覺得隨著時間推移,這些都會逐漸減少,也會有幫助。”

結合我們在文章開頭所列舉的,從UMC 到格羅方德,再到美光三星海力士,幾乎所有的晶圓廠運營利潤都在受益于AI 革命,英特爾卻還在大談成本攤銷和利潤。

也許從這一點我們能看到,英特爾可能會將18A 作為自家產品未來幾年的主力節(jié)點,而14A 作為面向代工用戶的先進節(jié)點,并且英特爾并不會像臺積電一樣,新工藝瞄準6 個月后開始貢獻利潤,而是可能將盈虧平衡點放在工藝推出后的24 個月之后,這可是不是代工業(yè)務傳統(tǒng)的模式,難道陳立武真的在等待羅唯仁來拯救英特爾的制造業(yè)務嗎?

噢,對了,英特爾制造業(yè)務現(xiàn)在最大的吸引力除了擁有國資背景之外,大概就是被成為美國半導體先進工藝最后底牌的EMIB 和Foveros 技術了,至于這兩個技術能不能帶得動英特爾的晶圓廠,感覺有點100 馬力坦克的既視感。

(本文來源于《EEPW》202512)

評論