聯發科創意 自建AI超算中心

先進制程芯片設計成本動輒數億美元,其中人力成本逾五成,另有相當比例來自EDA工具與反復驗證流程。 晶片業者透露,導入AI后,可在短時間內生成大量布局與繞線方案,透過算法自動優化功耗、效能與面積(PPA),加速「設計收斂」,并降低流片(Tape-out)風險。 形成用AI設計AI芯片,再用AI芯片加速AI的正向循環,逐漸成為業界共識。

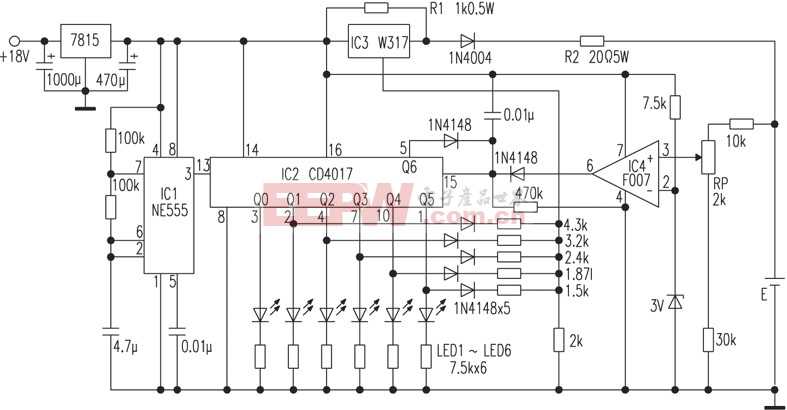

IC設計業積極進軍,聯發科與創意已開始投入算力基礎建設。 創意所打造《圖靈中心》將于今年啟用。 該中心位在苗栗竹南,于去年已陸續投入逾20億元打造機電工程及不斷電系統,隨客戶對ASIC需求提升,強化高功耗運算環境與電力備援,顯示其對未來AI ASIC設計與驗證量能的高度重視。

聯發科則斥資百億元,于苗栗銅鑼科學園區興建資料數據中心。 據供應鏈指出,今年7月將完成第一期第二階段之機電工程,未來將采用英偉達AI服務器系統; 市場解讀,此舉不僅為內部AI研發所需,更是強化自有芯片設計能力的重要戰略投資。

業者分析,當芯片設計進入高度自動化階段,算力即成核心競爭力。 擁有自建數據中心,可支持多版本芯片并行模擬與驗證,加快SoC與客制化ASIC開發節奏,對手機、車用與數據中心芯片皆具關鍵意義。

AI導入設計流程后,芯片開發將形成「模型優化芯片、芯片再優化模型」循環。 未來芯片架構可依特定工作負載快速調整,從云端推理、邊緣運算到機器人與自駕系統,都能透過更短的設計周期實現定制化。

此外,AI輔助設計也可能改寫產業分工。 傳統Fabless模式強調設計與制造分離,未來則可能進一步走向高度自動化設計,人力重心轉向架構定義與系統整合。 對臺系IC設計而言,掌握AI設計能力與自有算力,將成為下一階段競爭門檻。

聯發科、創意運算中心投資

評論