設計使用開源工具的芯片:Silicluster 的發展

在半導體設計領域,從零開始學習芯片設計的難度往往被低估,工具與知識層面的雙重壁壘令人望而卻步。但隨著開源軟硬件計劃的興起,想要迎接這一挑戰的開發者迎來了新的機遇。

本文詳細闡述了 Silicluster 芯片的全設計流程 —— 這款芯片全程基于開源工具開發,核心設計理念為易獲取性與高性價比(見圖 1)。

圖 1:Silicluster、Silicluster Plus 及 Silicluster Pro 芯片規格書,展示三款芯片的各自核心特性

芯片設計之路的開端

踏上芯片設計之路,實屬偶然。自兒時起,我便對各類事物的工作原理充滿好奇,卻從未想過這份好奇心會演變成對電子學的熱愛。我的學術生涯先后完成了電子工程本科、電子設計碩士的學習,最終取得了同領域的博士學位。

但在后續的研究中,我深刻意識到,傳統芯片設計工具的高昂成本與使用門檻成為了一大難題。在墨西哥的眾多科研機構中,由于高端設計工具的授權費用高得令人卻步,相關人員根本無法接觸到這類工具。

這一現狀促使我開始探索開源工具 —— 這類工具有望打破半導體設計的壁壘,而 Silicluster 芯片的研發也由此誕生。這款芯片的設計初衷,是為學生、教育工作者以及小型企業打造一款價格親民、易于獲取的芯片產品。

工具的安裝與學習

研發過程中遇到的第一個難題,便是所需開源工具的安裝。與擁有官方技術支持和完善文檔的傳統商用電子設計自動化(EDA)工具不同,使用開源工具更像是一場 “自助探索”。這是我首次接觸各類開源工具:用于從寄存器傳輸級(RTL)到版圖數據庫(GDS)流程的 OpenLane,以及用于原理圖繪制的 Xschem。盡管沒有官方的支持體系,但活躍的開源社區與可查閱的文檔,讓我得以順利入門。

安裝過程的繁雜是最大的挑戰之一:每款工具都有不同的依賴環境,即便完成安裝,想要熟練運用還需跨過一道學習門檻。但這份付出最終收獲了豐厚的回報,Magic、Netgen 以及 OpenLane 等開源工具,讓我能夠以遠低于傳統方案的成本,完成定制化芯片的設計與制造。

整個學習過程耗時良久,但開源社區的協作屬性讓這段經歷變得更有價值。如今,得益于社區的知識共享與共同努力,這些開源工具的安裝已變得相對簡便,整體使用流程也順暢了許多。

設計選型:打造 Silicluster 芯片

在確定芯片設計方向時,我的目標是打造一款能成為各類項目基礎的芯片產品。最初的構想是,設計一款可集成多個小型模塊(最多支持 256 個獨立電路)、且能靈活處理數字和模擬信號的芯片,Silicluster 芯片也因此應運而生。

這款芯片的核心定位,是打造一個低成本開發平臺:讓多位開發者共享制造成本,同時各自開展獨立的項目研發。芯片采用多路復用架構,每個研發項目對應的專用集成電路(ASIC)或多路復用器,均通過次級多路復用器實現連接,最終由一個中央多路復用器完成通路選擇。該架構支持集成最多 16 個獨立功能模塊,實現了芯片面積的優化利用。

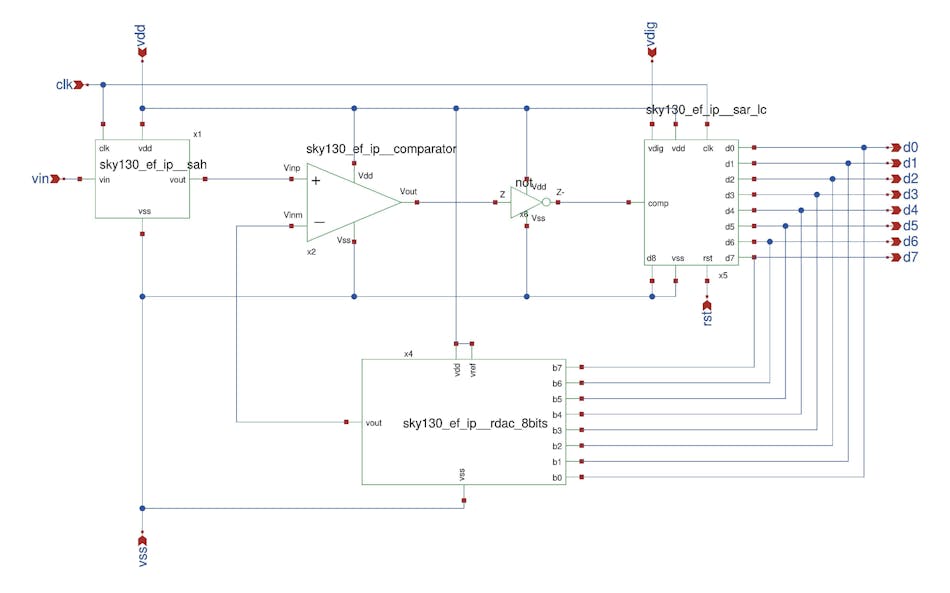

芯片設計的核心模塊為8 位逐次逼近寄存器型(SAR)ADC,負責將模擬信號轉換為數字信號(見圖 2)。

圖 2:8 位 SAR 型 ADC 的原理圖

為實現芯片數字與模擬模塊的兼容,配套設計了 8 位 DAC 模塊作為補充(見圖 3)。

圖 3:8 位 DAC 的原理圖

可在單一設計中同時集成模擬和數字電路,是 Silicluster 芯片最具吸引力的特性之一。這一特性為開發者提供了更多可能性,無需為不同功能單獨設計芯片,即可搭建復雜的系統。

Silicluster 芯片的核心技術支撐

Silicluster 芯片基于 SkyWater 公司的 130 納米工藝制程設計,該工藝是開源半導體項目的高性價比之選,兼具實用性與經濟性。130 納米工藝與開源工具的結合,大幅降低了芯片設計與制造的相關成本。

值得一提的是,本次研發過程中還有一個重要的中間協作方 ——Efabless 公司,該公司為設計者與芯片制造工廠搭建了溝通的橋梁。借助 Efabless 的平臺,我得以利用現有的芯片制造基礎設施,且無需承擔傳統設計模式的高昂成本。這次合作,是 Silicluster 芯片及其他相關項目能夠落地的關鍵。

電路設計的學習過程

Silicluster 芯片的設計,要求我既要掌握電路設計的基本原理,也要熟悉打造一款數模混合信號芯片所需的各類細節。為做好設計準備,我查閱了經典的專業書籍與線上資源,例如 Allen 和 Holberg 所著的《CMOS Analog Circuit Design》,深入理解模擬電路的設計難點。

同時,我也學習了數字邏輯設計的相關教程與文檔,重點研究了電路各組件之間的交互邏輯。這段學習經歷讓我深刻認識到,讓電路的每個模塊都實現高效工作,是芯片設計的核心要點。

本次設計的一大挑戰是,需在芯片嚴苛的面積限制下,設計出一款分辨率達標的 ADC(見圖 4),同時兼顧低功耗要求(見圖 5、圖 6)。

圖 4:8 位 SAR 型 ADC 的仿真驗證圖

圖 5:基于 Magic 工具設計的 8 位 SAR 型 ADC 版圖

圖 6:8 位 SAR 型 ADC 的等軸測視圖

設計流程:原理圖繪制、仿真驗證、版圖設計

在充分理解電路設計要求后,我正式進入了芯片的設計流程。第一步是使用 Xschem 工具完成原理圖繪制。這一過程既充滿成就感,也伴隨著諸多困擾 —— 設計中需要為每個組件的配置做出大量決策。

原理圖繪制完成后,我使用 ngspice 工具進行仿真驗證,確保電路能夠實現預期功能,圖 7 為 DAC 模塊的仿真驗證結果。仿真驗證能夠有效發現各類問題,例如信號完整性問題、組件配置錯誤等,這些問題都可能影響芯片的最終功能。

圖 7:8 位 DAC 的仿真曲線圖

當原理圖通過仿真驗證后,設計進入版圖設計階段。這一階段的挑戰尤為突出,需要將設計好的電路適配到極小的芯片面積中。面積限制雖為設計創新提供了動力,卻也造成了諸多設計瓶頸。

版圖設計中,不僅要保證各組件的正確連接,還需通過合理布局最大限度減少組件間的干擾、提升芯片性能。這一過程需要經過多次迭代優化,因為每一個版圖設計決策,都會影響后續的所有設計步驟(見圖 8、圖 9)。

圖 8:基于 Magic 工具設計的 8 位 DAC 版圖

圖 9:8 位 DAC 的等軸測視圖

版圖設計完成后,我使用 Magic 和 OpenLane 工具完成后續的關鍵步驟:設計規則檢查(DRC)、版圖與原理圖一致性檢查(LVS),以及 GDSII 格式文件的生成。每個步驟都需要細致把控,確保最終的設計方案能夠順利完成制造,無任何工藝錯誤。

整個設計流程中,最難的部分是在芯片有限的面積內完成所有設計的調整與優化。為了兼顧芯片的面積、功耗與功能,我需要不斷反復修改設計,這一過程雖令人疲憊,卻是確保芯片能在實際場景中正常工作的必要環節。

經驗總結與改進方向

Silicluster 芯片的設計過程復雜卻極具價值,這段經歷讓我收獲了諸多寶貴經驗,其中最重要的是迭代優化與周密規劃的重要性。現在回頭來看,若能在設計初期投入更多時間優化芯片架構,使其更好地適配版圖設計的限制,后續便能節省大量的時間 —— 研發中曾多次因面積限制而返工修改設計。

另一大收獲是,使用開源工具設計芯片,需要足夠的耐心與創新思維。研發過程中,我多次向開源社區尋求支持,無論是通過論壇、GitHub 的問題反饋區,還是查閱海量的技術文檔。讓各類開源工具協同高效工作的過程,讓我深刻體會到堅持與協作的價值。

未來規劃

展望未來,計劃繼續優化 Silicluster 芯片,為其集成更多新功能。核心目標是提升芯片的能效,同時探索更先進的制造工藝,例如采用更先進的制程,或集成更復雜的數模轉換機制。此外,還將整理一套詳盡的教程,幫助更多人運用這些開源工具設計屬于自己的芯片,讓芯片設計變得更易上手。

除了優化現有芯片,也有諸多新的項目構想,例如研發一款面向物聯網(IoT)應用的新型低功耗微控制器芯片。這款芯片將以 Silicluster 芯片的設計經驗為基礎,針對特定市場做更精準的設計。

最終思考:是否推薦嘗試?

對于有數字或模擬電路設計經驗的開發者,強烈推薦嘗試使用開源工具設計芯片。這一過程雖最初看似艱難,但帶來的學習價值是無價的,更是拓展知識、積累半導體設計實操經驗的絕佳方式。

對于零基礎的初學者,建議先從簡單的項目入手,再嘗試挑戰 Silicluster 這類復雜的芯片設計。但無論是否有設計經驗,如今豐富的開源工具與資源,都讓芯片設計變得比以往任何時候都更易獲取、更貼近大眾。

評論