MOSFET失效分析

MOSFET 是芯片的基本單元,MOSFET是為了實現數字電路中0和1的開關,他有三個電極,源極、柵極和漏極,簡化模型如下 圖

MOSFET的制造過程中,源極、柵極和漏極的布局與連接至關重要。這些組成部分的精細工藝,決定了MOSFET的性能與可靠性。在邏輯門的構建中,MOSFET與其他晶體管協同工作,共同實現各種邏輯功能。

運算器的構建離不開邏輯門的巧妙組合。這些邏輯門,如同電路中的關鍵節點,通過精確的開關動作,共同構建出運算器的復雜功能。

最終,這些精心構建的邏輯門被整合到一個僅有一枚指甲大小的芯片之中。

為何需要“電子開關”?

想象一下老式的電燈開關:按下去,金屬片接觸,電路接通,燈亮;抬起來,金屬片斷開,電路斷開,燈滅。這種機械開關簡單可靠,但在飛速運轉的手機、電腦芯片里,它們太慢了、太大、太耗電,根本無法勝任。

我們需要一種開關:

(1) 速度極快:每秒能開關數十億次。

(2) 體積超小:比頭發絲還細,能在指甲蓋大小的芯片上集成幾十億個。

(3) 耗電極低:開關動作本身幾乎不耗電。

(4) 控制靈敏:能用微小的電信號來控制大電流的通斷。

MOSFET正是這樣的“超級電子開關”。

下面對MOS失效的原因總結以下六點:

1:雪崩失效(電壓失效),也就是我們常說的漏源間的BVdss電壓超過MOSFET的額定電壓,并且超過達到了一定的能力從而導致MOSFET失效。

2:SOA失效(電流失效),既超出MOSFET安全工作區引起失效,分為Id超出器件規格失效以及Id過大,損耗過高器件長時間熱積累而導致的失效。

3:體二極管失效:在橋式、LLC等有用到體二極管進行續流的拓撲結構中,由于體二極管遭受破壞而導致的失效。

4:諧振失效:在并聯使用的過程中,柵極及電路寄生參數導致震蕩引起的失效。

1、雪崩失效(電壓型失效)當 MOSFET 漏源極之間施加的電壓超過器件額定漏源擊穿電壓BVdss,且超出幅度達到臨界閾值時,會引發雪崩擊穿效應,導致器件內部載流子急劇倍增,最終造成 MOSFET 永久性失效。

2、SOA 失效(電流型失效)該失效源于器件工作狀態超出安全工作區(SOA)范圍,分為兩種情況:一是漏極電流 Id 直接超出器件規格書中的最大限值,引發瞬時過載失效;二是 Id 過大導致導通損耗、開關損耗劇增,熱量累積速度超過器件散熱能力,最終因熱擊穿失效。

3、體二極管失效在橋式拓撲、LLC 諧振拓撲等需要體二極管續流的電路中,體二極管若承受超出耐受能力的反向恢復電流、電壓尖峰,或長時間高頻續流導致熱應力持續累積,會造成體二極管損壞,進而引發 MOSFET 整體功能失效。

4、諧振失效多顆 MOSFET 并聯應用場景下,柵極驅動回路的寄生電感、寄生電容,與器件自身的輸入電容等參數相互作用,會引發高頻寄生振蕩。這會導致柵極電壓波動劇烈,器件開關過程異常,最終因損耗激增或電壓擊穿失效。

5、靜電失效秋冬干燥環境或靜電防護措施不足時,人體、生產設備產生的靜電電荷可通過柵極等引腳注入器件,瞬間擊穿柵極氧化層,造成 MOSFET 不可逆損壞。

6、柵極電壓失效柵極遭遇異常過沖電壓尖峰,超出柵源極額定耐壓范圍(多數商用 MOSFET 柵源耐壓為 ±20V 左右),會直接擊穿柵極氧化層,導致柵極絕緣性能完全喪失,器件徹底失效。

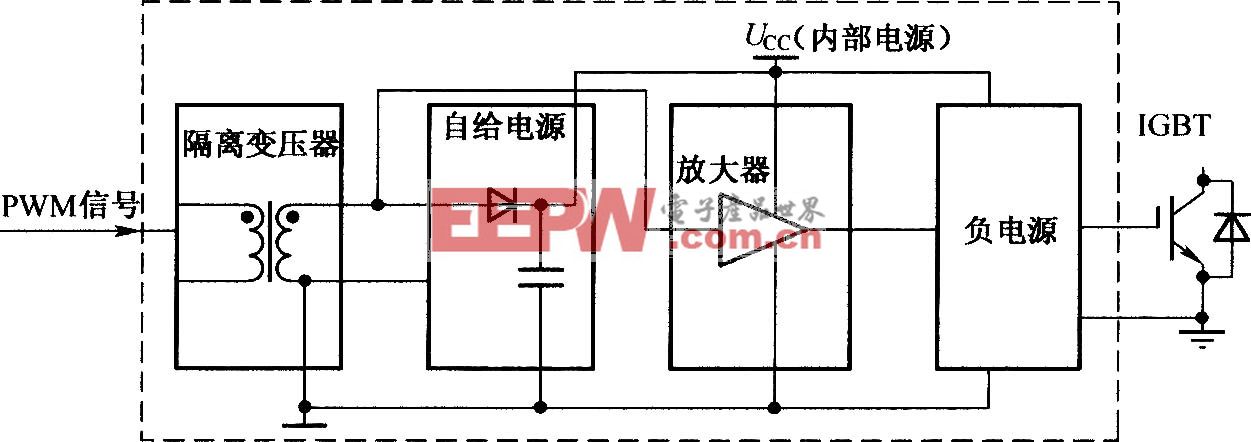

7、驅動異常失效該失效分為兩種子類型:一是驅動不足,柵源驅動電壓 Vgs 未達到器件導通閾值或未達到飽和導通電壓,導致 MOSFET 導通電阻 Rds(on) 大幅上升,損耗飆升引發熱失效;二是驅動過沖,柵極驅動回路的電壓尖峰超出柵源耐壓,與柵極電壓失效原理類似,但觸發源為驅動電路設計缺陷,而非外部異常電壓。

8、熱循環失效MOSFET 在工作過程中反復經歷 “升溫 - 降溫” 的熱循環,會導致器件封裝引腳與芯片結合處、焊點出現熱疲勞,進而引發引腳松動、焊點開裂,最終造成電路接觸不良或器件失效。該失效多見于大功率、高頻開關的應用場景。

9、化學腐蝕失效在潮濕、含鹽霧或腐蝕性氣體的惡劣環境中,MOSFET 的封裝材料會被侵蝕,引腳會發生氧化、銹蝕,導致引腳接觸電阻增大;若腐蝕穿透封裝,還會造成芯片內部電路氧化短路,最終引發器件失效。

10、封裝失效因機械沖擊、振動、外力擠壓等物理因素,導致 MOSFET 封裝開裂、引腳彎折斷裂,使芯片與外部電路的連接中斷,或芯片直接暴露在空氣中受污染失效。

雪崩失效分析(電壓失效)

到底什么是雪崩失效呢,簡單來說MOSFET在電源板上由于母線電壓、變壓器反射電壓、漏感尖峰電壓等等系統電壓疊加在MOSFET漏源之間,導致的一種失效模式。簡而言之就是由于就是MOSFET漏源極的電壓超過其規定電壓值并達到一定的能量限度而導致的一種常見的失效模式。

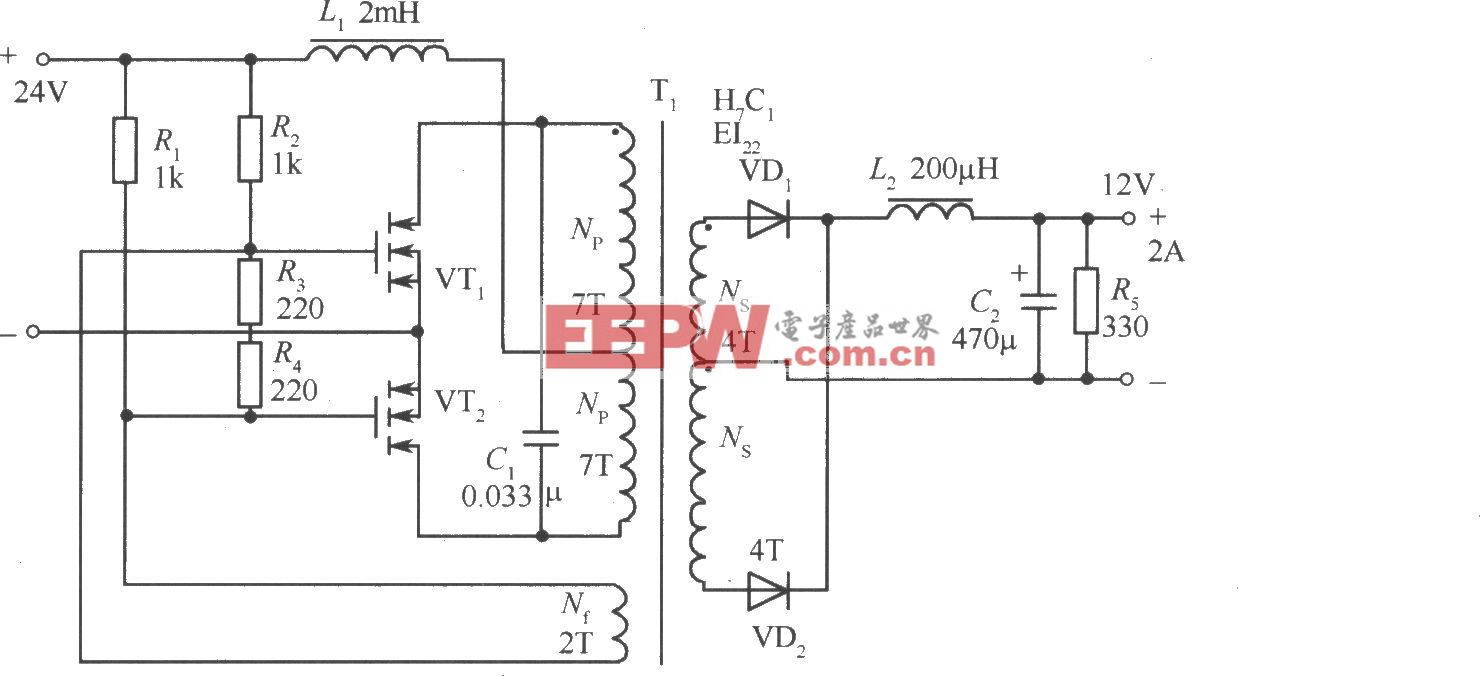

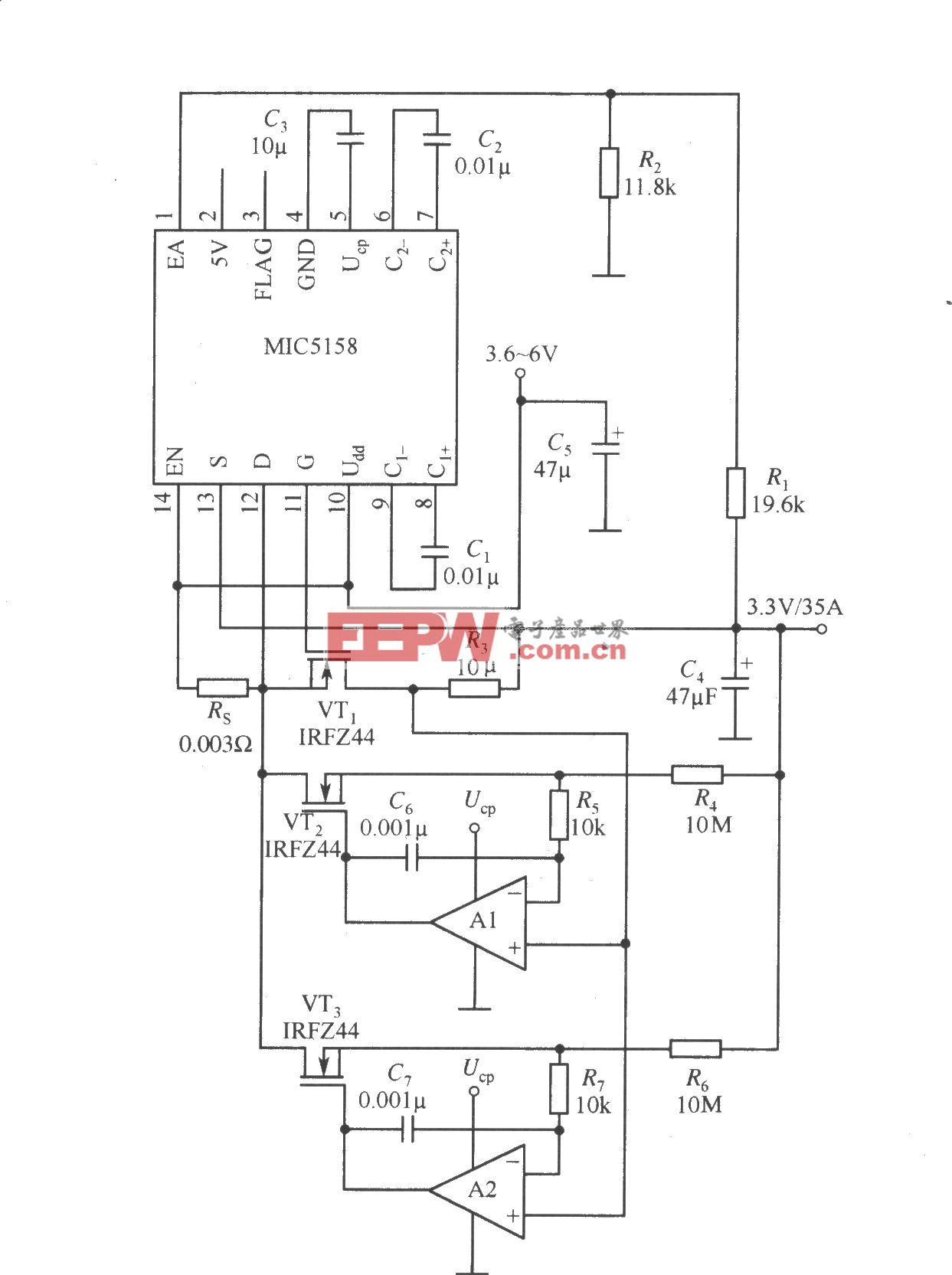

下面的圖片為雪崩測試的等效原理圖,做為工程師可以簡單了解下。

無鉗位感性開關測試(UIS):通過電感儲存能量,模擬雪崩工況

核心配置:VDD 供電、電感 L 儲能、RG 限流、示波器捕獲 Vds/Ids 波形

可能我們經常要求器件生產廠家對我們電源板上的MOSFET進行失效分析,大多數廠家都僅僅給一個EAS.EOS之類的結論,那么到底我們怎么區分是否是雪崩失效呢,下面是一張經過雪崩測試失效的器件圖,我們可以進行對比從而確定是否是雪崩失效。

1. 雪崩現象定義

當 MOSFET 漏源極電壓(Vds)超過擊穿電壓(BVdss)時,寄生 BJT 導通,形成雪崩電流,器件吸收能量并產生溫升

本質:漏區與襯底間 PN 結的雪崩擊穿效應

2. 雪崩損壞機制

局部元胞過熱:能量集中導致芯片局部溫度超過 150℃

寄生 BJT 導通:引發 MOSFET 誤導通,加劇電流沖擊

典型失效表現:Source 極底部燒毀、柵氧化層擊穿

關鍵參數與測試基礎

1. 核心雪崩參數

關鍵計算公式

電源浪涌問題典型場景

1. 應用背景

設備:32W/28W LED 驅動電源(單端反激拓撲)

輸入條件:90~265VAC,浪涌要求 1200V DM

核心器件:LSD11N70、LSD07N65、TK13A65U 等 MOSFET

2. 三類典型失效場景

3. 失效波形示例(Surge Case 3)

測試條件:230Vac 輸入,1400V/90° 浪涌

關鍵數據:Vds=848V,Ids=5.8A,遠超器件安全閾值

波形特征:Vds 尖峰陡峭,Ids 沖擊電流明顯

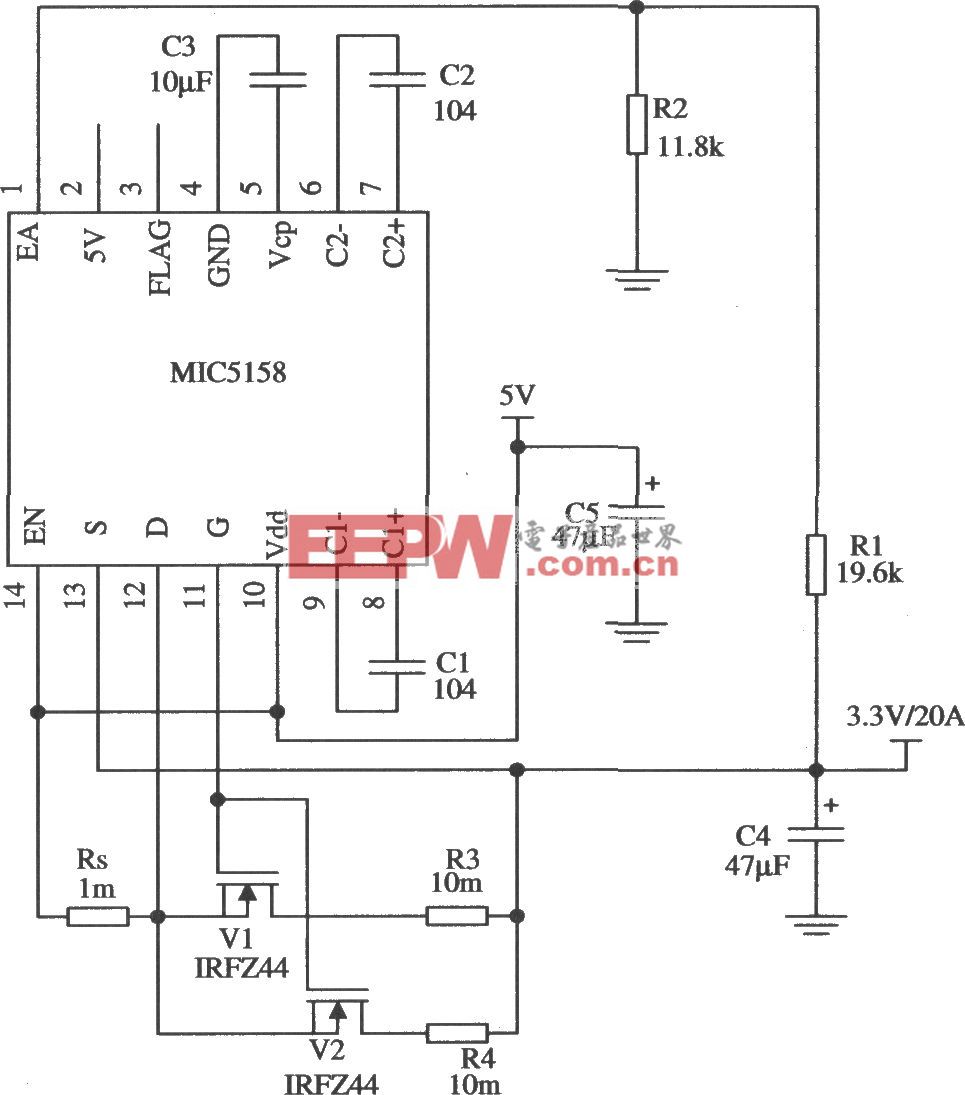

案例:28W LED 電源浪涌整改(原方案失效)

1. 原方案問題診斷

電源規格:輸入 90~265VAC,輸出 28~40VDC/700mA

失效現象:1300V 浪涌測試時 MOSFET 擊穿

核心原因:

母線殘壓過高,Vds 峰值接近 BVdss

變壓器飽和導致雪崩電流激增(Ids=11.25A)

浪涌能量未有效吸收

整改前:Vds 尖峰突出,Ids 沖擊明顯

整改后:Vds 平穩,Ids 無尖峰,能量分布均勻

效率:全電壓范圍保持 88% 以上,與原方案基本一致

功率因數:整改后 PF≥0.94,滿足行業標準

可靠性:1000 次浪涌測試無失效,通過率 100%

雪崩失效的預防措施

雪崩失效歸根結底是電壓失效,因此預防我們著重從電壓來考慮。具體可以參考以下的方式來處理。

1:合理降額使用,目前行業內的降額一般選取80%-95%的降額,具體情況根據企業的保修條款及電路關注點進行選取。

2:合理的變壓器反射電壓。

3:合理的RCD及TVS吸收電路設計。

4:大電流布線盡量采用粗、短的布局結構,盡量減少布線寄生電感。

5:選擇合理的柵極電阻Rg。

6:在大功率電源中,可以根據需要適當的加入RC減震或齊納二極管進行吸收。

SOA失效(電流失效)

再簡單說下第二點,SOA失效

SOA失效是指電源在運行時異常的大電流和電壓同時疊加在MOSFET上面,造成瞬時局部發熱而導致的破壞模式。或者是芯片與散熱器及封裝不能及時達到熱平衡導致熱積累,持續的發熱使溫度超過氧化層限制而導致的熱擊穿模式。

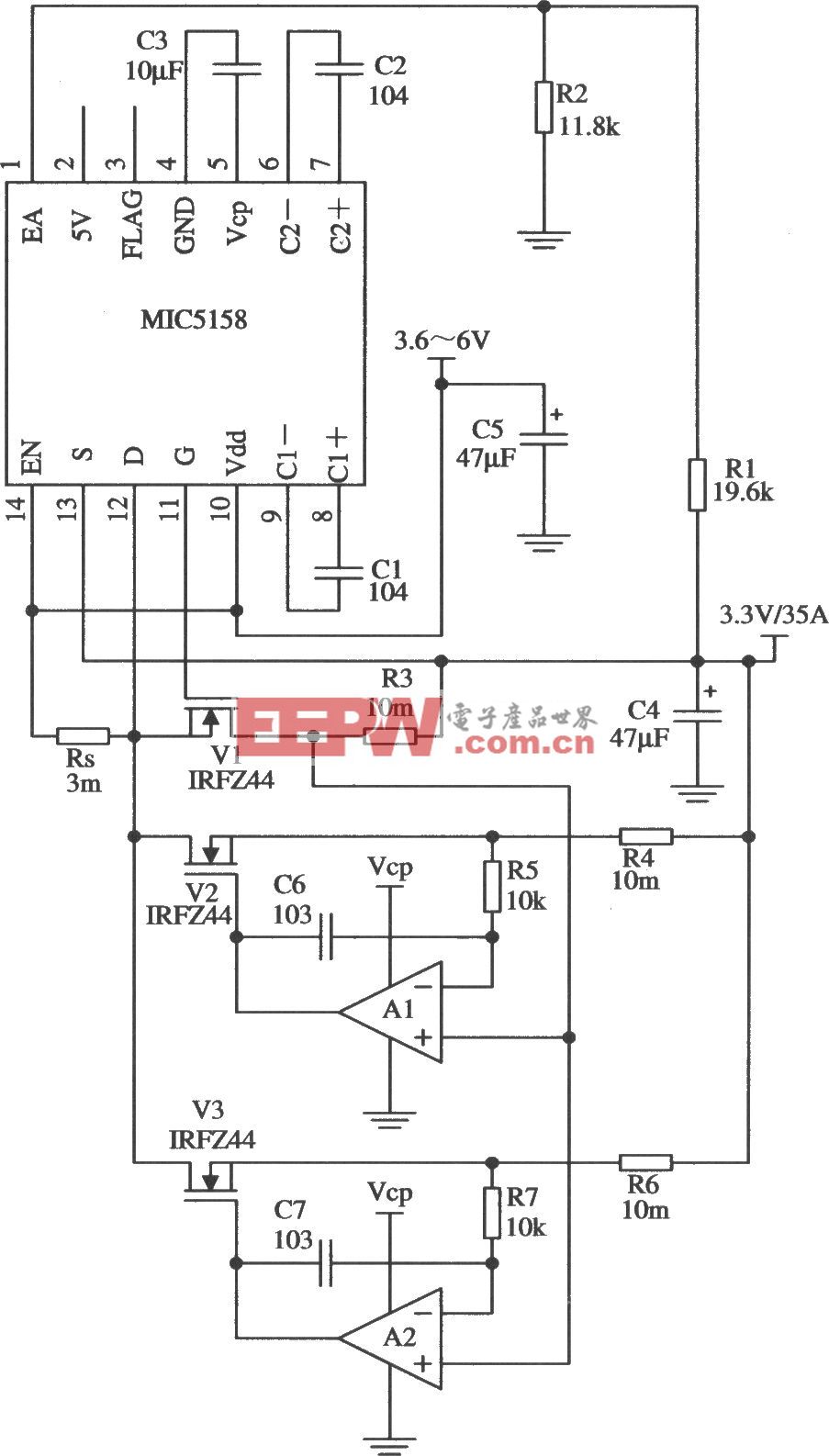

關于SOA各個線的參數限定值可以參考下面圖片。

1:受限于最大額定電流及脈沖電流

2:受限于最大節溫下的RDSON。

3:受限于器件最大的耗散功率。

4:受限于最大單個脈沖電流。

5:擊穿電壓BVDSS限制區

我們電源上的MOSFET,只要保證能器件處于上面限制區的范圍內,就能有效的規避由于MOSFET而導致的電源失效問題的產生。

這個是一個非典型的SOA導致失效的一個解刨圖,由于去過鋁,可能看起來不那么直接,參考下。

SOA失效的預防措施:

1:確保在最差條件下,MOSFET的所有功率限制條件均在SOA限制線以內。

2:將OCP功能一定要做精確細致。

在進行OCP點設計時,一般可能會取1.1-1.5倍電流余量的工程師居多,然后就根據IC的保護電壓比如0.7V開始調試RSENSE電阻。有些有經驗的人會將檢測延遲時間、CISS對OCP實際的影響考慮在內。但是此時有個更值得關注的參數,那就是MOSFET的Td(off)。它到底有什么影響呢,我們看下面FLYBACK電流波形圖(圖形不是太清楚,十分抱歉,建議雙擊放大觀看)。

從圖中可以看出,電流波形在快到電流尖峰時,有個下跌,這個下跌點后又有一段的上升時間,這段時間其本質就是IC在檢測到過流信號執行關斷后,MOSFET本身也開始執行關斷,但是由于器件本身的關斷延遲,因此電流會有個二次上升平臺,如果二次上升平臺過大,那么在變壓器余量設計不足時,就極有可能產生磁飽和的一個電流沖擊或者電流超器件規格的一個失效.

評論